8086 interrupt

An interrupt is the method of processing the microprocessor by peripheral

device. An interrupt is used to cause a temporary halt in the execution of program.

Microprocessor responds to the interrupt with an interrupt service routine, which is

short program or subroutine that instructs the microprocessor on how to handle the

interrupt.

There are two basic type of interrupt, maskable and non-maskable, non-

maskable interrupt requires an immediate response by microprocessor, it usually used

for serious circumstances like power failure. A maskable interrupt is an interrupt that

the microprocessor can ignore depending upon some predetermined condition defined

by status register.

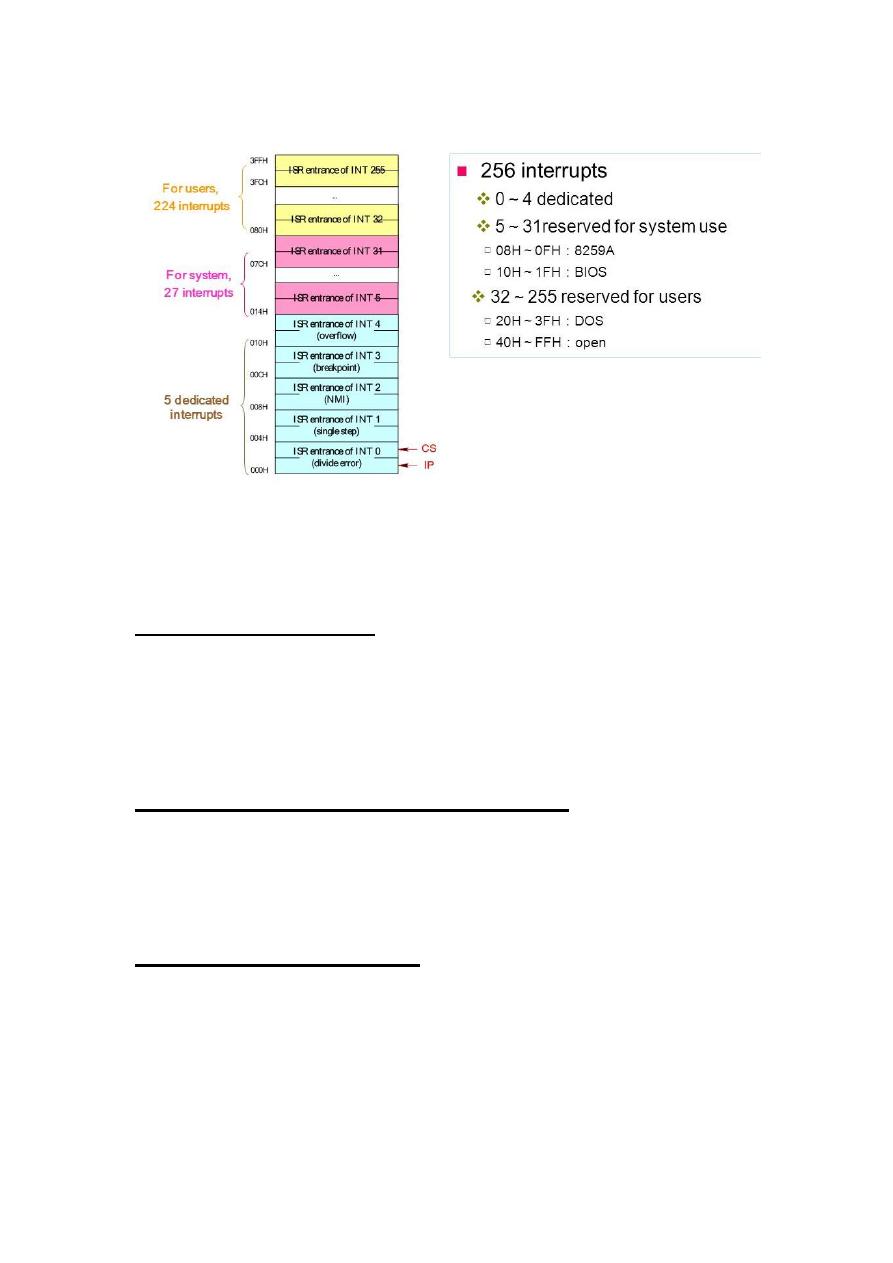

Hardware,software and internal interrupt are service on priority basis. each

interrupt is given a different priority level by assign it a type number. Type 0

identifies the highest-priority and type 255 identifies the lowest- priority interrupt.

The 8086 chips allow up to 256 vectored interrupts. This means that you can

have up to 256 different sources for an interrupt and the 8086 will directly call the

service routine for that interrupt without any software processing.

When an interrupt occurs regardless of source, the 8086 does the following:

1. The CPU pushes the flags register onto the stack.

2. The CPU pushes a far return address (segment:offset) onto the stack, segment value

first.

3. The CPU determines the cause of the interrupt (i.e., the interrupt number) and

fetches the four byte interrupt vector from address 0:vector*4.

4. The CPU transfers control to the routine specified by the interrupt vector table

entry.

When the interrupt service routine wants to return control, it must execute an

IRET (interrupt return) instruction. The interrupt return pops the far return address

and the flags off the stack. Note that executing a far return is insufficient since that

would leave the flags on the stack.

Interrupt Vector Table - IVT

•

8086 Recognizes 256 Different Interrupts Specified by Type Number or Vector

• 1 Byte of Data Must Accompany Each Interrupt Specifies Type Vector is Pointer

into Interrupt Vector Table, IVT

– Stored in Memory from 0000:0000 to 0000:03ffh

• IVT Contains 256 Far Pointer Values

– Far Pointer is CS:IP Values

• Each Far Pointer is Address of Interrupt Service Routine, ISR

– Also Referred to as Interrupt Handler.

Interrupt Vector Table - IVT

hardware interrupt

The primary sources of interrupts, however, are the PCs timer chip, keyboard,

serial ports, parallel ports, disk drives, CMOS real-time clock,

mouse, sound cards, and other peripheral devices. These devices connect to an Intel

8259A programmable interrupt controller (PIC) that prioritizes the interrupts and

interfaces with the 8086 CPU.

NON-MASKABLE INTERRUPT (NMI)

The processor provides a single non-maskable interrupt pin (NMI) which has

higher priority than the maskable interrupt request pin (INTR). The NMI is edge-

triggered on a LOW-to-HIGH transition. The activation of this pin causes a type 2

interrupt.

MASKABLE INTERRUPT

Whenever an external signal activates the INTR pin, the microprocessor will

be interrupted only if interrupts are enabled using set interrupt Flag instruction. If the

interrupts are disabled using clear interrupt Flag instruction, the microprocessor will

not get interrupted even if INTR is activated. That is, INTR can be masked.