א

א

אאא

ã¹]<gè…‚jÖ]æ<ËÖ]<Üé×Ãj×Ö<íÚ^ÃÖ]<퉉ö¹]

אאא

א

٧٤١

٧٤١

א

א

א

٧٤١

א

א

א

،،אא،א

W

אאאאאאאאאא

א א א א א

א א ،א

אאאאאא

،אאאאאא

א

אא

K

אאאאאאא

א،אאא

א،

אאאאאא

א،אאאא

אאאאאאאאאאאאא

א א ،א

אא،אא

K

אא

?

א

?

?

?

א

אאאאאא

K

אאאאאאא

،א،אאאא

אאאאא

K

،אאאא

א

K

אאאא

٧٤١

א

א

א

אאאא

KKK

،

א،אאאאאא

אאא

K

אאאאא

א

א،אא،אאאא

אאאאאאאא

אאא

K

א

אאאא

،אאאאא،אאא

،אאא

אאא

אאאא

אאאא

K

אאאאא

אאא

א

אאאא

K

א

אאאא،אא

אא،א،אא

K

אאאא،

،

א

אא

א،א

אא

K

،א

KKKKKK

אא

אא

א

א

אאא

ã¹]<gè…‚jÖ]æ<ËÖ]<Üé×Ãj×Ö<íÚ^ÃÖ]<퉉ö¹]

אאאא

א

א

١

אאא

אא

W

•

אא

א

K

•

אא

K

•

אאאאאאא

K

•

אאאאא

K

•

אאאאא

K

١

J

١

Introduction

א

א

K

אאאאא

)

Binary Number System

(

אאאאאאא

)

Digital Electronic Circuits

(

K

אא،אאאא

)

Decimal Number System

(

א

K

אאא

אאאאאא

)

Octal Number System

(

אאא

)

Hexadecimal Numbering System

(

K

אאאאאאא

אאאאאאא

K

א

א

א

אאאאאאא

K

אאאאא

W

١K

א

K

٢K

אאא

K

٣K

אאאאאא

K

٤

K

א

אאא

K

٥

K

אאאאא

K

אאאא

)

Digit

(

א

)

Number

(

،

)

Symbol

(

אאאאא

،א

)

٠{١{٢{٣{٤, ... , ٨{٩

(

אאא

אאאאאאאא،אא

אאא،א

)

٤١

(

אאא

)

٣٢١

(

،א

אאא

א

)

٤١

(

)

١،٤

(

אאא

א

)

٣٢١

(

)

١،٢،٣

(

)

٦

(

א

א

K

١

J

٢

אאא

Decimal Numbering System

אאאאאאא

א

אאאא

K

אאאא

)

٠١

(

א

٠١

)

٠١

(

٠{١{٢{٣{٤{٥{٦{٧{٨{٩

K

אא

)

Positional Weight

(

אא

)

٨٢١

(

א

א

)

٨

(

אא

F

א

E

،א

אאא

١

)

٨× ١ = ٨

(

אא،

)

٢

(

אא

F

אא

E

אאא

٠١

)

٢× ١٠ = ٢٠

(

،

אא

F

١

E

אא

F

א

E

אאא

٠٠١

)

١× ١٠٠ = ١٠٠

(

K

א

،אאאאא

W

(

١× ١٠٠) + (٢ × ١٠) + (٨ × ١) = ١٠٠ + ٢٠ + ٨ = ١٢٨

אאא

F

٠١

E

אא

אאאא

٠١

٠١

٠

=

١

W

........

٠١

٥

٠١

٤

٠١

٣

٠١

٢

٠١

١

٠١

٠

א

٨٢١

W

١

٢

٨

אאאא

٠١

٢

٠١

١

٠١

٠

١× ١٠

٢

+

٢× ١٠

١

+

٨× ١٠

٠

()٨٢١

٠١

=

٠٠١+ ٢٠ + ٨

אא

)

٨٢١

(

אא

٠١

א

א

)

Subscript

(

אאאא

K

אאאאאא

א

٠١

١

W

٠١

٢

٠١

١

٠١

٠

• ٠١

١

٠١

٢

٠١

٣

........

١

J

٣

אאא

Binary Numbering System

אאאא

א

)

٢

(

)

٢

(

א

)

١،٠

(

.

אאאאאאא

)

٢

(

W

.....

٢

٤

٢

٣

٢

٢

٢

١

٢

٠

אאאא

W

.....

١ ٢ ٤ ٨ ٦١

אא

)

١٠٠١١

(

W

٢

٤

٢

٣

٢

٢

٢

١

٢

٠

١ ٠ ٠ ١ ١

= (

١× ٢

٤

) + ( ١× ٢

٣

) + ( ٠× ٢

٢

) + ( ٠× ٢

١

) + ( ١× ٢

٠

)

= ٦١+ ٨ + ٠ + ٠ + ١ = (٢٥)

٠١

אא،אאאאא

אאאאאא

(

)٢

אא

אא

(

)١٠٠١١

٢

K

אאאאא

W

■

אא

)

Bit

(

W

אא

(Bit)

א

)

Binary Digit

(

אא

אאא

K

אאא

F

א

E

א

א،אא

(

)١٠٠١

٢

)

٤-bits

(

א

(

)١٠١١٠١١

٢

)

٧-bits

(

א

K

אא

(Decimal Point)

■

אא

)

Number of Binary Combinations

(

W

אא

א

אאא

)

bits

(

K

אאא

W

N =

n

2

W

N

=

אאא

n

=

א

)

bits

(

אא

()٢

אא

W

N = ٢

٢

= ٤

אא

()٣

אא

W

N = ٢

٣

= ٨

אא

()٤

אא

W

N

=

٢

٤

= ٦١

אאאאא

K

■

אא

)

Bit

(

W

אאא

א

אאא

٢

٠

)

١

(

()١

א

אאא

٢

١

()٢

א

٢

٢

()٤

א

K

אאאאא

אא

אאא،אאא،אא

)

it

B

ignificant

S

east

L

(

א

א

)

LSB

(

אאא

אאאא

)

it

B

ignificant

S

ost

M

(

אא

)

MSB

(

K

■

א

)

Byte

EW

אא

)

Bit

(

אאא

אאאאא،אאאא

)

٠

(

אא

)

١

(

א

א

F

E

אאא

אאא

K

א

א

א

א

K

א

)

Byte

(

אאאא

K

אא

א

W

١byte = ٨ bits

١

J

٤

אאאאא

Decimal-to-Binary Conversion

אאאא،אאא

)

Sum of Weights Method

(

אא

אא

)

٢

(

)

Repeated Division–by– ٢Method

(

אאא

אאא

K

١

J

٤

J

١

אאאאאא

אא

٠١

)

٤١

(

،א

א

٤١

٢

א،

א

٢

א

)

٠

.(

אאאאאא

K

אאא

)

LSB

(

אאאא

)

MSB

(

אא،

W

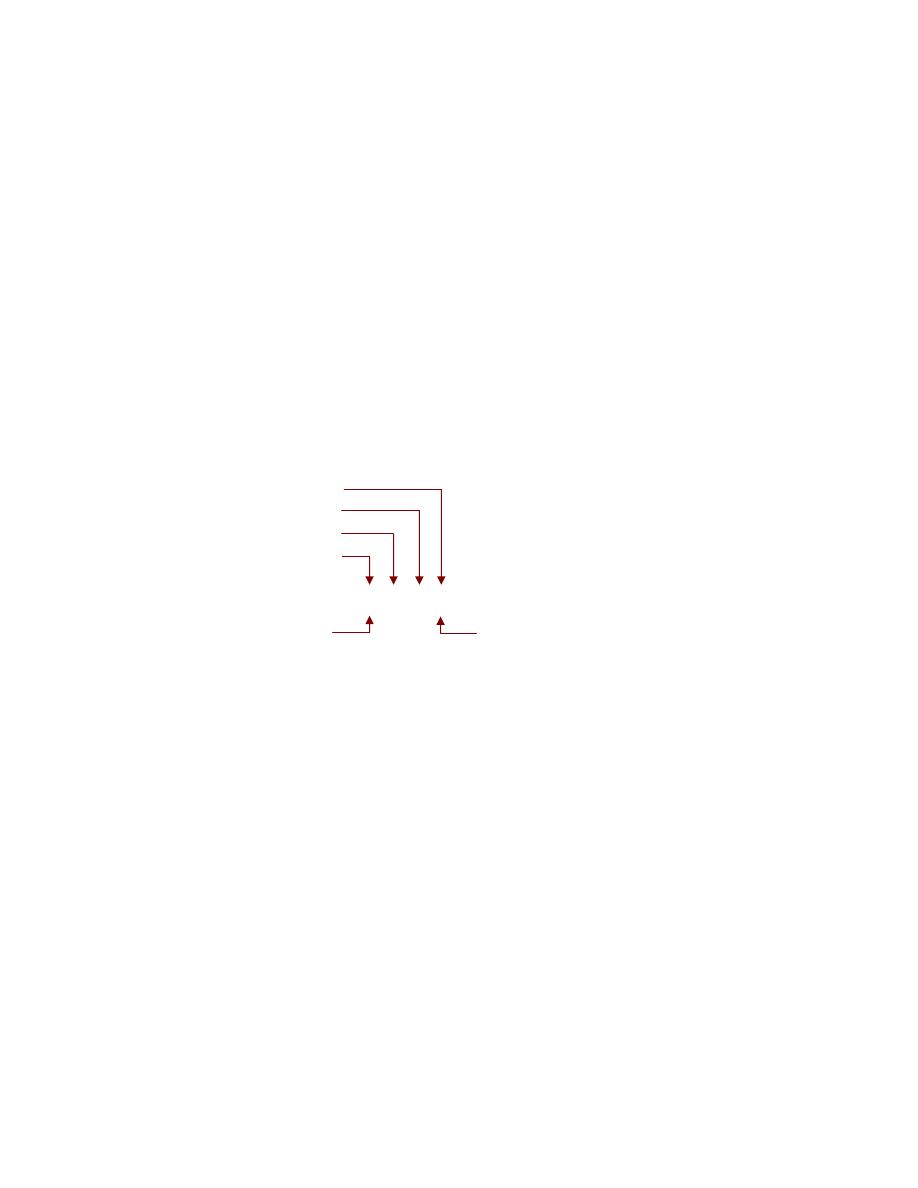

٤١÷ ٢ = ٧

٠

٧÷ ٢ = ٣

١

٣÷ ٢ = ١

١

١÷ ٢ = ٠

١

٠ ١ ١ ١

(MSB) (LSB)

W

()٤١

٠١

= ()٠١١١

٢

F

١

J

١

WE

אא

()٥٢

٠١

א

K

א

W

א

א

א

٥٢÷ ٢ = ١٢

( ١LSB)

٢١÷ ٢ = ٦

٠

٦÷ ٢ = ٣

٠

٣÷ ٢ = ١

١

١÷ ٢ = ٠

( ١MSB)

א

W

()٤١

٠١

= ()٠١١١

٢

F

١

J

٢

WE

אא

()٧٨

٠١

א

K

א

W

٧٨÷ ٢ = ٤٣

( ١LSB)

٣٤÷ ٢ = ٢١

١

١٢÷ ٢ = ١٠

١

٠١÷ ٢ = ٥

٠

٥÷ ٢ = ٢

١

٢÷ ٢ = ١

٠

١÷ ٢ = ٠

( ١MSB)

א

W

()٧٨

٠١

= ()١١١٠١٠١

٢

١

J

٤

J

٢

אאאאא

אאאאאא

אא

()٢

K

אאא

)

Decimal Fractions

(

אא

אא

()٢

K

אא

)

٥٢١٣٫٠

(

אא

אא

٥٢١٣٫٠

()٢

אאא،

()٢

אאא

()٠

אאאא

K

אא

)

Carried Digits

(

אאאא

אאאא

א

K

אאא

)

MSB

(

אאא

)

LSB

(

K

א

W

٥٢١٣٫٠

× ٢= ٠٫٦٢٥

٠

א

א

٥٢٦٫٠

× ٢= ١٫٢٥

١

٥٢٫٠

× ٢= ٠٫٥

٠

٥٫٠

× ٢= ١٫٠٠

١

(LSB)

( ٠ ١ ٠ ١MSB)

F

١

J

٣

WE

אא

()٥٢٫٩٣

٠١

א

K

א

W

אאאאא

()٢

W

٩٣÷ ٢ = ١٩

( ١LSB)

٩١÷ ٢ = ٩

١

٩÷ ٢ = ٤

١

٤÷ ٢ = ٢

٠

٢÷ ٢ = ١

٠

١÷ ٢ = ٠

( ١MSB)

א

W

()٩٣

٠١

= ()١١١٠٠١

אאאא

()٢

W

٥٢٫٠

× ٢= ٠٫٥

٠

٥٫٠

× ٢= ١٫٠٠

١

W

()٥٢٫٠

٠١

= ()١٠٫٠

٢

אאא

W

()٥٢٫٩٣

٠١

= ()١٠٫١١١٠٠١

٢

١

J

٥

אאאאא

Binary-to-Decimal Conversion

אא

אאאאא

()٢

אאאא

٦١, ٨, ٤, ٢, ١

א

K

אאא

א

אא

)

Bit

(

אא

()١

אאאאאא

K

אאא

W

F

١

J

٤

WE

אא

١٠٠١٠١١

א

K

א

W

()١

אא

אא

W

٢

٦

٢

٥

٢

٤

٢

٣

٢

٢

٢

١

٢

٠

:

א

١ ٠ ٠ ١ ٠ ١ ١:

אא

=

١× ٢

٦

+ ١× ٢

٥

+ ٠× ٢

٤

+ ١× ٢

٣

+ ٠× ٢

٢

+ ٠× ٢

١

+ ١× ٢

٠

= ٤٦+ ٣٢ + ٨ + ١ = (١٠٥)

٠١

אאאאאא

ﺧﺎﻧ ﺎت

)

Bits

(

אא

)

Binary Point

(

אאאאא

אא

)

Decimal Point

(

אא

אאאא

W

……٢

٤

٢

٣

٢

٢

٢

١

٢

٠

• ٢

-١

٢

-٢

٢

-٣

٢

-٤

…….

אא

F

١

J

٥

WE

אאא

()١١٠١٫٠

٢

א

K

א

W

• ٢

-١

٢

-٢

٢

-٣

٢

-٤

٠

• ١ ١ ٠ ١

∴()١١٠١٫٠

٢

=

١

× ٢

-١

+ ١× ٢

-٣

+ ١× ٢

-٤

= ٥٫٠+ ٠٫١٢٥ + ٠٫٠٦٢٥ = (٠٫٦٨٧٥)

٠١

١

J

٦

אאאא

Binary Arithmetic

אאאאאא

אא

K

אאאאא

K

١

J

٦

J

١

אא

Binary Addition

אאא،אאאא

)

Binary Digits

(

W

٠+ ٠ = ٠

٠+ ١ = ١

١ + ٠ = ١

١ + ١ = ٠carry

F

א

E

١

⇒ = ٠١

אאא

אאא،אא

١+ ١= ١٠

()٢

אא،

()١

אאאאא

אאא

K

אאאא

W

F

١

J

٦

WE

אא

١١٠, ١١٠

K

א

W

אאאא

W

١

١

٦

١

١

٠

+

٣+ ٠

١

١

F

E

٩

١

٠

٠

١

F

١

J

٧

WE

אאא

١١٠, ١٠٠

K

א

W

٤

١

٠

٠

+

٠ ٣

١

١

F

E

٧

١

١

١

١

J

٦

J

٢

אא

Binary Subtraction

אא

W

١

J

אא

א

K

٢

J

אא

K

אא،אא

K

א

אא

F

א

E

אאאאאא

אאאאא

א

W

٠– ٠= ٠

١

١– ٠ = ١

١– ١= ٠

٠ – ١= ١ (

)١

א

(

)١

א

אאא

W

•

אא

K

•

א

אאא

אאאאא

W

()٠

()٠

()١

()١

א

()٠

K

()٠

()١

א

()١

K

()١

()٠

א

()١

()٠

אא

F

א

E

()١

()١

()٠

K

אאאאא

K

F

١

J

٨

WE

אאא

()١٠١

אא

()١١٠

K

א

W

٠

א

١

٠

١

א

١

١

٠

–

٠

١

٠

١

J

٧

אאאאא

One's and Two's Complements of Binary Numbers

אאאאאאא

K

א

אאאאאאאא

K

אא

)

١

(

)

٠

(

)

٠

(

)

١

(

א

א

W

א

(

١)

אא

א

(

٠١)

(

١)

א

(

١)

א

(

١)

א

(

٠)

אא

١ ١ ٠ ٠ ١ ١ ٠ ١

אא

٠ ٠ ١ ١ ٠ ٠ ١ ٠

אאא

א

W

אא

W

אא

K

א

()١

א

אאאא

W

אא

Z

אא

+

١

אא

אא

١١٠٠١١٠١

K

אאא

()١

אא

K

אא

١ ١ ٠ ٠ ١ ١ ٠ ١

אא

٠ ٠ ١ ١ ٠ ٠ ١ ٠

()١

١

+

אא

٠ ١ ١ ١ ٠ ٠ ١ ٠

אא

W

אאאא

)

LSB

(

אא

)

٠

(

אא

אאאאא

א

אאאא

א

F

אאאאאא

אאאא

אא

E

،

אא

()١٠١١٠١٠١

٢

אא

W

אא

١ ٠ ١ ١ ٠ ١ ٠ ١

אא

١ ١ ٠ ٠ ١ ٠ ١ ٠

١

J

٨

אאא

א

Representation of Signed Numbers

א

אאאאאאא

אאא

אאאאאא

אא

א،א

()٠

،א

()١

א

K

אאא

אאאא

אאאא

)

Sign Bit

(

א

א

)

Magnitude

.(

אא

אאאאאא

W

אא

)

Sign-Magnitude

(

אא

)

١'s Complement

(

אא

)

٢'s Complement

.(

١

J

٨

J

١

אא

)

Sign-Magnitude System

(

אא

،אא

אא

)

Bit

(

אאא

אאאאאא

K

א

אאאאא

א

אאא

אא

K

אא

(+)٣٢

אא

א

W

١ ١ ١ ٠ ١ ٠ ٠ ٠

אא

(-)٣٢

ﻓﺈﻧﻨﺎ

W

١

١

١

٠

٠

١

٠

٠

١

אאא

(+)٣٢

،

(–)٣٢

א

K

١

J

٨

J

٢

אא

)

١'s Complement System

(

אאאאאאאאאא

אא

K

אאא

אאא

א

K

אא

(–)٣٢

אאא

W

א

)

+٣٢

(

١

١

١

٠

١

٠

٠

٠

א

)

٣٢

–

(

٠

٠

٠

١

٠

١

١

١

אאאאאאאא

א

K

١

J

٨

J

٣

אא

)

٢'s Complement

(

אא

אאאאא

א

אא

K

אאאאאא

K

אא

(-)٣٢

אאא

(+)٣٢

W

א

(Sign Bit)

אא

(Magnitude Bits)

א

(Discard carry)

א

)

+٣٢

(

١

١

١

٠

١

٠

٠

٠

א

)

٣٢

-

(

١

٠

٠

١

٠

١

١

١

אאאאאאא

K

١

J

٩

אאאאאא

Arithmetic Operations with Signed

Numbers

אאאא

،

אאאאאאאא

،

אא

F

١

J

٦

KE

א

א

אאאאאא

אא

אאא

K

אאאאאאא

א

W

F

١

J

٩

WE

א

אא

٠١١١٠٠٠٠

אא

٠١٠١١١١١

אאאא

K

א

W

א

W

٤١– (– ٦) = ٤١+ ٦ = ٢٠

א

W

٠ ١ ١ ١ ٠ ٠ ٠ ٠

א

(

H )٤١

+ ٠ ١ ١ ٠ ٠ ٠ ٠ ٠

א

א

(

H )٦

٠ ٠ ١ ٠ ١ ٠ ٠ ٠

א

(

H )٠٢

F

١

J

٠١

WE

אאאאאא

W

()٠٠٠١٠٠٠٠

٢

– ()٠٠١٠٠٠٠٠

٢

א

W

א

W

٨– ٤ = ٨+ (-٤) = ٤

W

٠ ٠ ٠ ١ ٠ ٠ ٠ ٠

א

(

H )٨

+ ٠ ٠ ١ ١ ١ ١ ١ ١

אא

(

)٤

٠ ٠ ١ ٠ ٠ ٠ ٠ ٠ ١

א

(

H )٤

F

١

J

١١

WE

אאאאאא

K

()١١١٠٠١١١

٢

– ()١٠٠١٠٠٠٠

٢

א

W

א

W

א

(Discard carry)

–

٥٢– (+٩) = – ٥٢– ٩ = -٣٤

W

١ ١ ١ ٠ ٠ ١ ١ ١

א

(

)٥٢

+ ١ ١ ١ ٠ ١ ١ ١ ١

אא

(

)٩

٠ ١ ١ ١ ١ ٠ ١ ١ ١

א

(

)٤٣

١

J

٠١

אאא

The Octal Numbering System

אאאא

()٨

()٨

(٠،١،٢،٣،٤،٥،٦،٧)

אאאאאא

אאאאאא،אאא

אאאאאאאא

K

١

J

٠١

J

١

אאאא

Octal-to-Decimal Conversion

אאאא

אאא

()٨

(……٨

٣

٨

٢

٨

١

٨

٠

)

،א

אאאא

)

…... ١ ٨ ٤٦ ٢١٥

(

،א

K

אא

אאא

אאא

K

אאא

()٥٧٢٢

٨

אא

W

אא

: ٨

٣

٨

٢

٨

١

٨

٠

אא

: ٥ ٧ ٢ ٢

∴ ()٥٧٢٢

٨

= ( ٢

× ٨

٣

) + ( ٢

× ٨

٢

) + ( ٧

× ٨

١

) + ( ٥

× ٨

٠

)

= ( ٢

× )٢١٥+ (٢ × ٦٤) + (٧ × ٨) + (٥ × ١)

= ٤٢٠١+ ١٢٨ + ٥٦ + ٥ = (١٢١٣)

٠١

١

J

٠١

J

٢

אאאא

Decimal–to–Octal Conversion

אאא

א

אא

א

()٨

אאאאאאא،

()٨

()٢

K

١

J

٠١

J

٢

J

١

אאאאאא

אא

٠١

)

٠٥١

(

אא

א

٠٥١

()٨

אא

()٨

א

()٠

.

אאאאא

א

K

אא

אא

אאא

א

א

اﻟﺤﺎﻣﻞ

)

LSD

(

igit}

D

ignificant

S

east

L

{

אאאא

igit}

D

ignificant

S

ost

M

{

)

MSD

(

אא

W

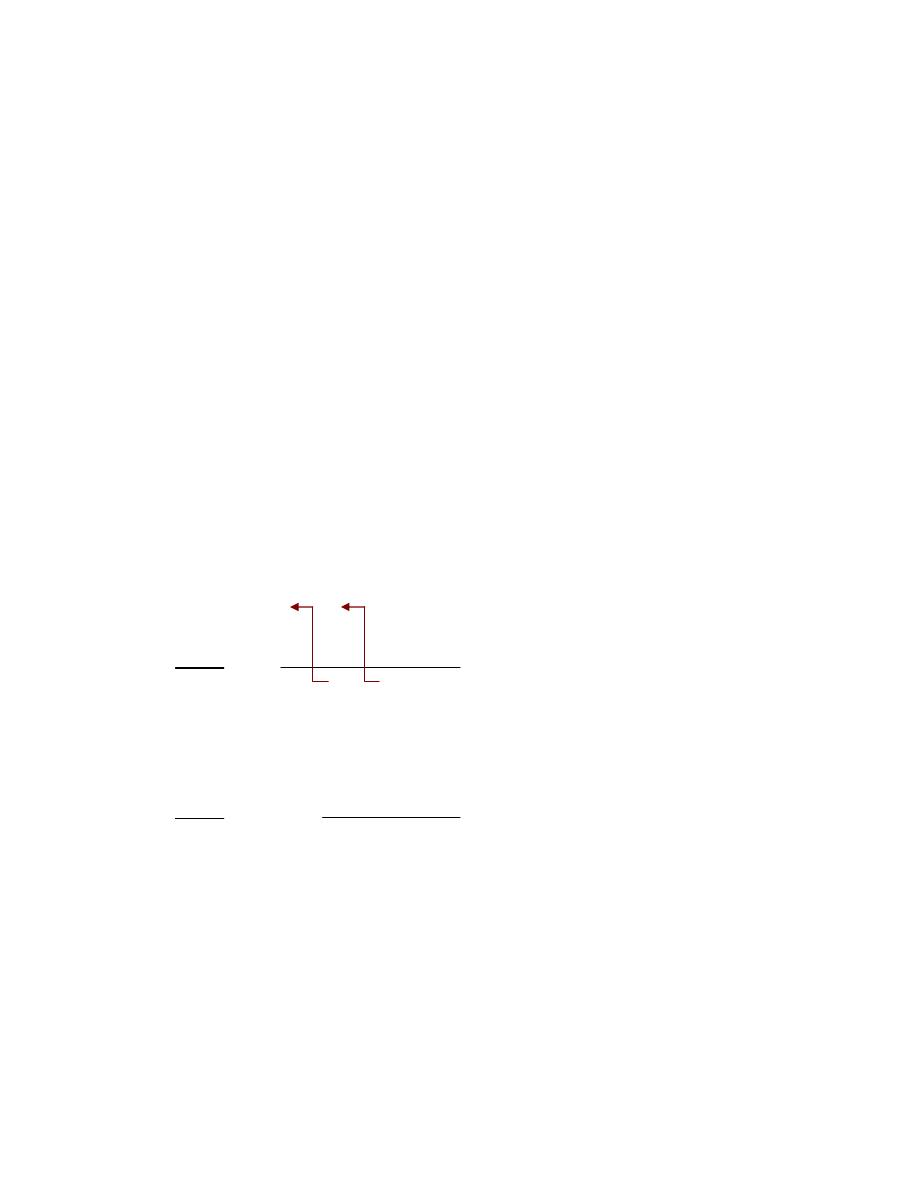

٠٥١÷ ٨ = ١٨

( ٦LSD)

٨١÷ ٨ = ٢

٢

٢÷ ٨ = ٠

( ٢MSD)

א

W

()٠٥١

٠١

= ()٦٢٢

٨

F

١

J

٢١

WE

אא

٠١

)

٤٢٦

(

אא

K

א

W

٤٢٦÷ ٨ = ٧٨

( ٠LSD)

٨٧÷ ٨ = ٩

٦

٩÷ ٨ = ١

١

١÷ ٨ = ٠

( ١MSD)

א

W

()٤٢٦

٠١

= ()١١٦

٨

١

J

٠١

J

٢

J

٢

אאאאא

אאא

אאאאא

אא

()٨

K

אא

)

٥٦٢٫٠

(

אא

אא

٥٦٢٫٠

(

)٨

،

אאא

()٨

אאא

()٠

אאא

א

K

א

א

)

Carried Digits

(

אאאאא

K

אאא

)

LSD

(

אא

)

MSD

(

א

W

٥٦٢٫٠

× ٨= ٢٫١٢

( ٢MSD)

٢١٫٠

× ٨= ٠٫٩٦

٠

٦٩٫٠

× ٨= ٧٫٦ ٨

٧

٨٦٫٠

× ٨= ٥٫٤٤

٥

٤٤٫٠

× ٨= ٣٫٥٢

٣

٢٥٫٠

× ٨= ٤٫١٦

٤

(LSD)

אאאאאא

()٦

אא

W

()٥٢٦٫٠

٠١

= ()٤٣٥٧٠٢٫٠

٨

א

اﻟﺤﺎﻣﻞ

F

١

J

٣١

WE

אא

٠١

)

٥٢٦٥٫٤٤

(

אא

K

א

W

אאאאא

()٨

K

٤٤÷ ٨ = ٥

( ٤LSD)

٥÷ ٨ = ٠

( ٥MSD)

א

W

()٤٤

٠١

= ()٤٥

٨

אאאא

()٨

W

٥٢٦٥٫٠

× ٨= ٤٫٥

٤

٥٫٠

× ٨= ٤٫٠٠

٤

W

()٥٢٦٥٫٠

٠١

= ()٤٤٫٠

٨

אאא

W

()٥٢٦٥٫٤٤

٠١

= ()٤٤٫٤٥

٨

١

J

٠١

J

٣

אאאאא

Octal-to-Decimal Conversion

אאאאאא

א

()٨

אאאא

٦٩٠٤, ٥١٢, ٦٤, ٨, ١

א

K

אא

אאא

)

Digit

(

א

אאא

א

K

אא

K

F

١

J

٤١

WE

אא

()٤٢٣

٨

אא

K

א

W

אא

: ٨

٢

٨

١

٨

٠

אא

: ٤ ٢ ٣

∴ ()٤٢٣

٨

= ( ٣

× ٨

٢

) + ( ٢

× ٨

١

) + ( ٤

× ٨

٠

)

= ( ٣

× )٤٦+ (٢ × ٨) + (٤ × ١)

= ٢٩١+ ١٦ + ٤ = (٢١٢)

٠١

אאאאאאאאא

אאא

)

Octal Point

(

אא

אאאא

W

……٨

٤

٨

٣

٨

٢

٨

١

٨

٠

• ٨

-١

٨

-٢

٨

-٣

٨

-٤

…….

אא

F

١

J

٥١

WE

אא

()٤١٫٧٦٥

٨

אא

K

א

W

אא

: ٨

٢

٨

١

٨

٠

• ٨

-١

٨

-٢

אא

: ٧ ٦ ٥

• ٤ ١

∴ ()٤١٫٧٦٥

٨

= ( ٥

× ٨

٢

) + ( ٦

× ٨

١

) + ( ٧

× ٨

٠

) + ( ١

× ٨

-١

) + ( ٤

× ٨

-٢

)

= ( ٥

× )٤٦+ (٦ × ٨) + (٧ × ١) + (١ × ٠٫١٢٥) + (٤ × ٠٫٠١٥٦٢٥)

= ٠٢٣+ ٤٨٠ + ٧ + ٠٫١٢٥ + ٠٫٠٦٢٥ = (٣٧٥٫١٨٧٥)

٠١

١

J

٠١

J

٤

אאא

אא

Octal-to-Binary Conversion

)

Digit

(

אא

)

٣-bits

(

،

אאאאא

K

א

א

F

١

J

١

KE

٧

٦

٥

٤

٣

٢

١

٠

אא

١١١

٠١١

١٠١

٠٠١

١١٠

٠١٠

١٠٠

٠٠٠

אא

F

١

J

١

E

אאא

K

אאא

א

K

F

١

J

٦١

WE

אא

()٧٥٣

٨

אא

K

א

W

()٧٥٣

٨

=

٣

٥

٧

١١١ ١٠١ ١١٠

= ()١١١١٠١١١٠

٢

F

١

J

٧١

WE

אא

()٣٤٥٫٦٧٢١

٨

א

K

א

W

()٣٤٥٫٦٧٢١

٨

=

١

٢

٧

٦

• ٥

٤

٣

٠١١ ١١١ ٠١٠ ١٠٠

• ١١٠ ٠٠١ ١٠١

= ()١١٠٠٠١١٠١٫٠١١١١١٠١٠١

٢

אאא

K

١

J

٠١

J

٥

אאאאא

Binary-to-Octal Conversion

אאאאאאאא

א

K

אא

–

J

אאא

א

אאא

אאאא

א

א

אאאא

K

F

١

J

٨١

WE

אא

()١٠١٠٠٫٠٠١١١٠١٠٠١١٠١

٢

אא

K

א

W

٠٠١ ١١٠ ١٠٠ ١١٠ ١٠٠

• ٠١٠ ١٠٠

١

٣

١

٣

٤

• ٢ ١

אאאאאא

W

()١٠١٠٠٫٠٠١١١٠١٠٠١١٠١

٢

= ()٢١٫٤٣١٣١

٨

١

J

٠١

J

٦

אאאא

Arithmetic Operations in Octal System

אאאא

K

١

J

٠١

J

٦

J

١

א

א

Octal Addition

אא

אאא

–

א

)

٠،٩

(

א

()٩

אאא،

()٩

א

()٠١

א

אאאאא

K

אא

א

אאאא

)

٠،١

(

אא

()٠١

אא

אאאא

K

א

אאאאאאאא

אאא

()٧

אאא

–

אאאא

()٧

א

()٠١

אאאאאא،א

)

١١, ١٢, ١٣, ١٤, ١٥, ١٦, ١٧

(

אאא

)

٠٢،٢١, ٢٢, ...... , ٢٧

(

אאא

)

٠٣, ٣١, ..... , ٣٧

(

א

K

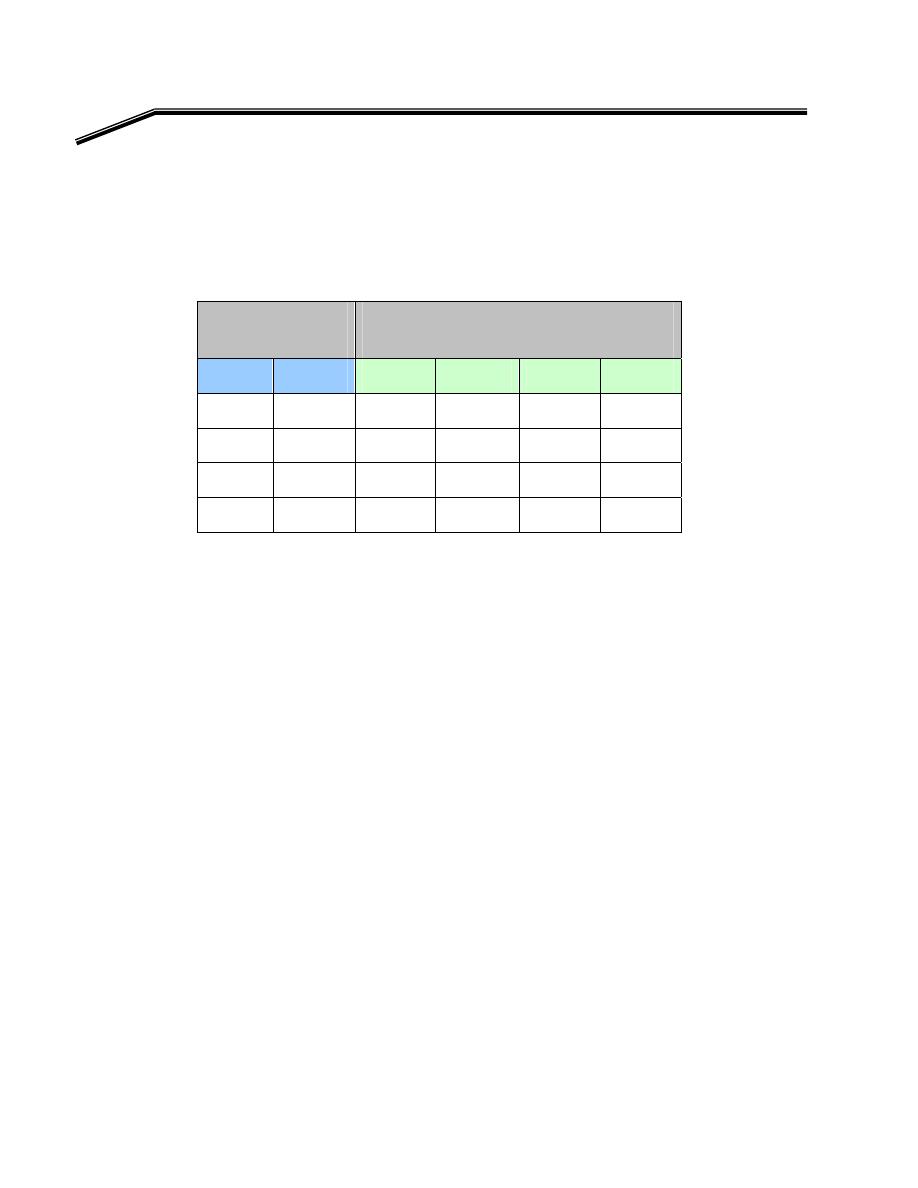

א

F

١

J

٢

E

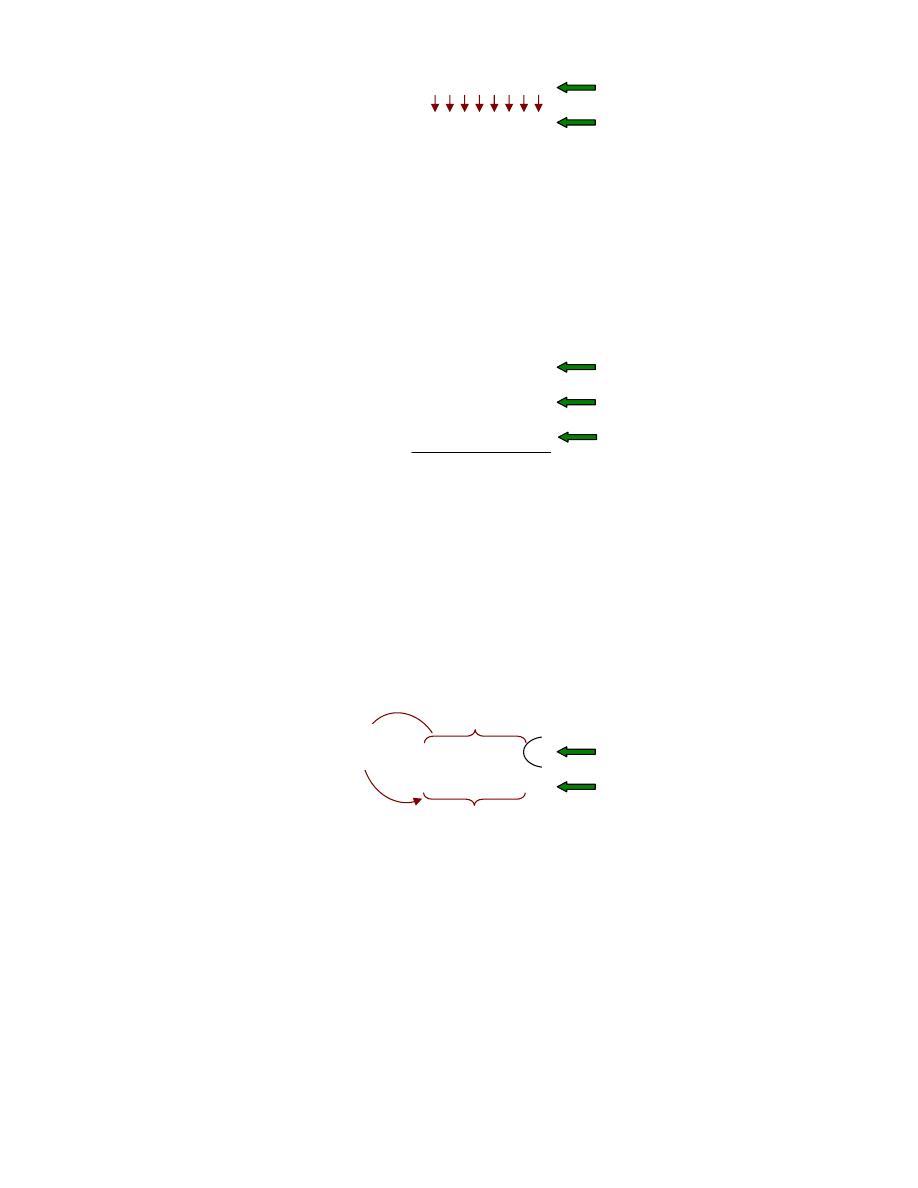

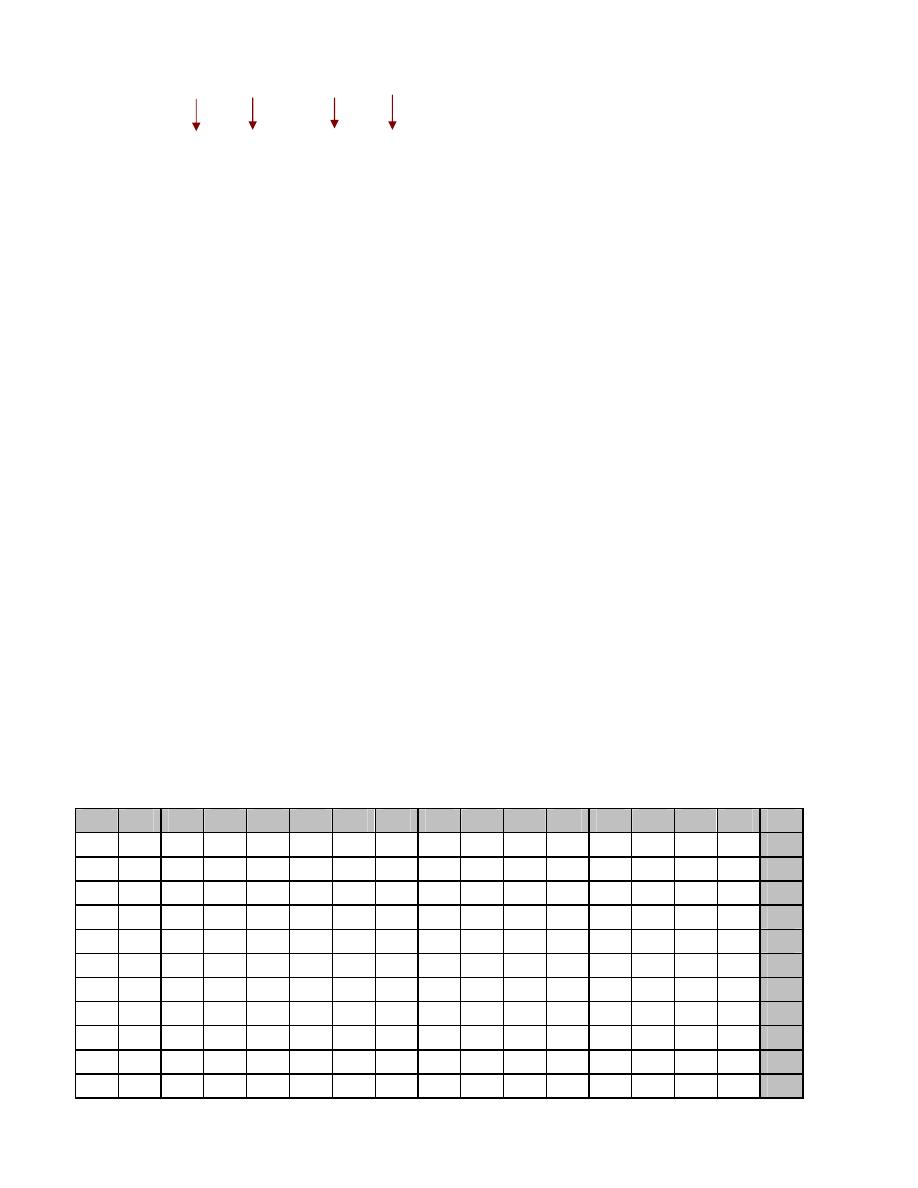

אאאאא

אאאאאאאא

אאא

אא

K

אא

א

W

•

אאאאאאא

()٧

K

•

אאא

()٧

אא

()٢

אא،א

()٧

אא

()٨

א

()٧

א

אא

()٠١

א

()٢

אא

אאא

F

אאאא

אאא

KE

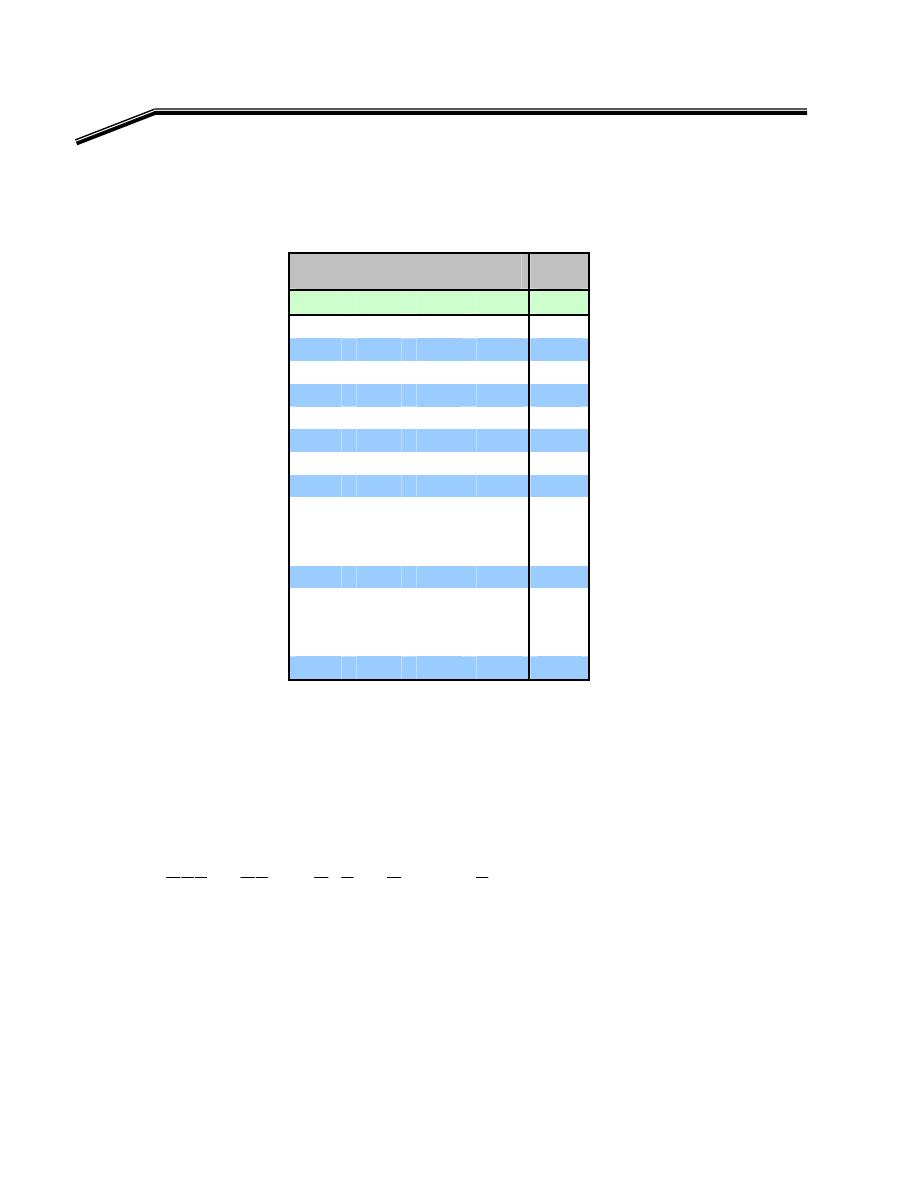

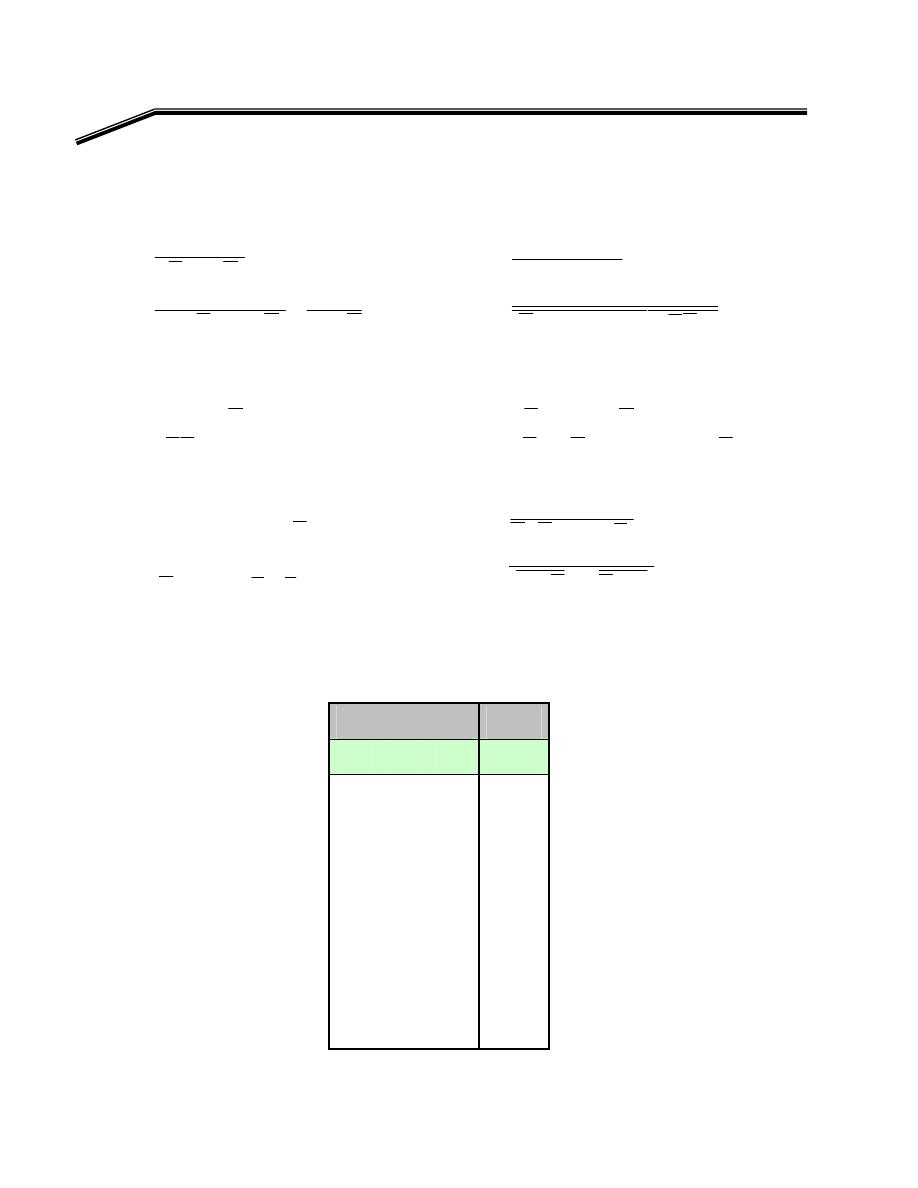

+

٠

١

٢

٣

٤

٥

٦

٧

٠

٠

١

٢

٣

٤

٥

٦

٧

١

١

٢

٣

٤

٥

٦

٧

٠١

٢

٢

٣

٤

٥

٦

٧

٠١

١١

٣

٣

٤

٥

٦

٧

٠١

١١

٢١

٤

٤

٥

٦

٧

٠١

١١

٢١

٣١

٥

٥

٦

٧

٠١

١١

٢١

٣١

٤١

٦

٦

٧

٠١

١١

٢١

٣١

٤١

٥١

٧

٧

٠١

١١

٢١

٣١

٤١

٥١

٦١

F

١

J

٢

E

אאא

K

F

١

J

٩١

WE

אאא

()٨٣

٨

،

()٢٤

٨

K

א

W

אא

W

٤٣

+ ٢٤

٦٧

∴()٤٣

٨

+ ()٢٤

٨

= ()٦٧

٨

אא

(٤،٢)

(٣،٤)

()٧

א

K

F

١

J

٠٢

WE

אאא

()٦٥

٨

،

()٣٦

٨

K

א

W

٦ ٥

+ ٣ ٦

١ ٤ ١

אאא

()٧

()٢

א

א

)

Carry

(

אא

K

١

J

٠١

J

٦

J

٢

אאא

Subtraction in Octal System

אאא

W

•

אא

אאא

K

•

אאא

()١

אא

–

אאא

()٨

אאאאאאא

אא

K

F

١

J

١٢

WE

אא

W

()٧٥٦

٨

– ()٦٤٣

٨

א

W

א

W

٧ ٥ ٦

א

– ٦ ٤ ٣

א

١ ١ ٣

∴()٧٥٦

٨

– ()٦٤٣

٨

= ()١١٣

٨

אאא

אא

K

F

١

J

٢٢

WE

אא

W

()٢٣٧

٨

– ()٤٣٦

٨

א

W

٢ ٣ ٧

א

– ٤ ٣ ٦

א

٦ ٧ ٠

∴()٢٣٧

٨

– ()٤٣٦

٨

= ()٦٧

٨

אא

()٤

()٢

אא

א

()١

א،אאאאאא

אא

א

()٣

()٢

אא

K

٦

١ ٢

א

١

J

١١

אאאא

Hexadecimal Numbering System

אאא

א

א

()٦١

)

٦١

(

א

)

٠،١،٢،٣،٤،٥،٦،٧،٨،٩,A,B,C,D,E,F

(

א

)

A,B,C,D,E,F

(

אא

(٠١, ١١, ١٢, ١٣, ١٤, ١٥)

א

K

١

J

١١

J

١

אאאא

Hexadecimal–to–Decimal Conversion

אאאאאאא

א

٦١

(……٦١

٣

٦١

٢

٦١

١

٦١

٠

)

א

אאא

)

... ٦١ ٦٥٢ ٦٩٠٤

١

(

א

אא

٦١

)

٩٣٫٢٢٥

(

W

אא

: ٦١

٢

٦١

١

٦١

٠

• ٦١

-١

٦١

-٢

אא

: ٢ ٢ ٥

• ٩ ٣

∴ ()٩٣٫٢٢٥

٦١

= ( ٥

× ٦١

٢

) + ( ٢

× ٦١

١

) + ( ٢

× ٦١

٠

) + ( ٣

× ٦١

-١

) + ( ٩

× ٦١

-٢

)

= ( ٥

× )٦٥٢+ (٢ × ١٦) + (٢ × ١) + (٣ × ٠٫٠٦٢٥) + (٩ × ٠٫٠٠٣٩٠٦٢)

= ٠٨٢١+ ٣٢ + ٢ + ٠٫١٨٧٥ + ٠٫٠٣٥١٥٥٨ = (١٣١٤٫٢٢٢٦٥٥)

٠١

אא

אאאא

K

א

אאא

()٦١

אא

K

١

J

١١

J

٢

אאאא

Decimal-to-Hexadecimal

Conversion

אאאא

אאאא

()٦١

אאאאאאאאאא

אא

()٦١

()٨

()٢

.

١

J

١١

J

٢

J

١

אאאאאאא

אא

٠١

)

٧٩

(

אא

א

٧٩

()٦١

אא

()٦١

א

()٠

K

אאאאא

אא

K

،אאא

אאא

)

LSD

(

אא

)

MSD

(

אא

W

٧٩÷ ١٦ = ٦

( ١LSD)

٦÷ ١٦ = ٠

( ٦MSD)

א

W

א

اﻟﺤﺎﻣﻞ

()٧٩

٠١

= ()١٦

٦١

F

١

J

٣٢

WE

אא

()٤١٣

٠١

אאא

K

א

W

٤١٣÷ ١٦ = ١٩ A (LSD)

٩١÷ ١٦ = ١

٣

١÷ ١٦ = ٠

( ١MSD)

א

W

()٤١٣

٠١

= (٣١A)

٦١

١

J

١١

J

٢

J

٢

אאאאאא

אאאאאאא

אא

א

()٦١

K

אא

()٥٢١٨٧٫٠

٠١

אאא

אא

()٦١

אא

א

()٦١

אאאאא

()٠

אאא

א

K

אאאאאא

אא

K

אאא

(LSD)

אאא

(MSD)

א

W

٥٢١٨٧٫٠

× ٦١= ١٢٫٥

C

٥٫٠

× ٦١= ٨٫٠٠

٨

W

∴()٥٢١٨٧٫٠

٠١

= (.٠C٨)

٦١

א

א

F

١

J

٤٢

WE

אא

()٢٥٫٩٢٣

٠١

אא

K

א

W

אאאאא

٦١

W

٩٢٣÷ ١٦ = ٢٠

( ٩LSD)

٠٢÷ ١٦ = ١

٤

١÷ ١٦ = ٠

( ١MSD)

א

W

∴()٩٢٣

٠١

= ()٩٤١

٦١

אא

()٦١

אא

W

٢٥٫٠

× ٦١= ٨٫٣٢ ٨ (MSD)

٢٣٫٠

× ٦١= ٥٫١٢ ٥

٢١٫٠

× ٦١= ١٫٩٢ ١

٢٩٫٠

× ٦١= ١٤٫٧٢ E

٢٧٫٠

× ٦١= ١١٫٥٢ B

٢٥٫٠

× ٦١= ٨٫٣٢ ٨ (LSD)

אאאאא

()٦

א

W

()٢٥٫٠

٠١

= (١٥٨٫٠EB٨)

٦١

אאא

W

()٢٥٫٩٢٣

٠١

= (١٥٨٫٩٤١EB٨)

٦١

١

J

١١

J

٣

אאאא

Hexadecimal-to-Decimal Conversion

אאאאאאא

א

()٦١

K

אאאאא

אא

K

אא

W

F

١

J

٥٢

WE

אאא

(F٩B)

٦١

אא

K

א

W

אא

: ٦١

٢

٦١

١

٦١

٠

אא

: F ٩B

∴ (F٩B)

٦١

= (F

× ٦١

٢

) + ( ٩

× ٦١

١

) + (B

× ٦١

٠

)

= ( ٥١

× )٦٥٢+ (٩ × ١٦) + (١١ × ١)

= ٠٤٨٣+ ١٤٤ + ١١ = (٣٩٩٥)

٠١

אאאאאאאאאאא

אאאאא

W

……٦١

٣

٦١

٢

٦١

١

٦١

٠

• ٦١

-١

٦١

-٢

٦١

-٣

…….

אא

F

١

J

٦٢

WE

אאא

(A.٥١C٣)

٦١

א

K

א

W

אא

: ٦١

٢

٦١

١

٦١

٠

• ٦١

-١

٦١

-٢

א

א

: A ٥ ١

• C ٣

∴ (A.٥١C٣)

٦١

= (A

× ٦١

٢

) + ( ١

× ٦١

١

) + ( ٥

× ٦١

٠

) + (C

× ٦١

-١

) + ( ٣

× ٦١

-٢

)

= ( ٠١

× )٦٥٢+ (١ × ١٦) + (٥ × ١) + (١٢ × ٠٫٠٦٢٥) + (٣ × ٠٫٠٠٣٩٠٦٢)

= ٠٦٥٢+ ١٦ + ٥ + ٠٫٧٥ + ٠٫٠١١٧١٨٦ = (٢٥٨١٫٧٦١٧)

٠١

١

J

١١

J

٤

אאאאא

Hexadecimal-to-Binary Conversion

אאאא

(٠،١،٢,……,٩,A,B,C,D,E,F)

אאא

(A,B,C,D,E,F)

אאאא

(٠١،١١،١٢،١٣،١٤،١٥)

K

אאאאא

אאא،אא

(٤-bits)

אא

F

١

J

٣

WE

F

١

J

٧٢

WE

א

(٣A٥)

٦١

א

K

א

W

(٣A٥)

٦١

=

٣A ٥

١٠١٠ ٠١٠١ ١١٠٠

= ()١٠١٠٠١٠١١١٠٠

٢

אא

אא

אאא

٠

٠٠٠٠

٠

١

١٠٠٠

١

٢

٠١٠٠

٢

٣

١١٠٠

٣

٤

٠٠١٠

٤

٥

١٠١٠

٥

٦

٠١١٠

٦

٧

١١١٠

٧

٨

٠٠٠١

٨

٩

١٠٠١

٩

٠١

٠١٠١

A

١١

١١٠١

B

٢١

٠٠١١

C

٣١

١٠١١

D

٤١

٠١١١

E

٥١

١١١١

F

F

١

J

٣

E

אאא

K

F

١

J

٨٢

WE

א

(B.٥٣D١)

٦١

אא

K

א

W

(B.٥٣D١)

٦١

= B

٥ ٣

• D ١

١٠١٠ ١١٠٠ ١١٠١

• ١٠٠٠ ١٠١١

= ()١٠٠٠١٠١١٫١٠١٠١١٠٠١١٠١

٢

١

J

١١

J

٥

אאאאא

Binary-to-Hexadecimal Conversion

אא

אאאא

אאאאאאא

אאאא

K

אאאאאא

אא

א

אאאא

K

F

١

J

٩٢

WE

אא

()١٠٠١٠١٫١٠١١١١٠١١

٢

אא

K

א

W

١٠١١ ١١٠١ ١٠٠٠

• ٠٠١٠ ٠١٠١

١

B

D

• A

٤

אאא

K

∴()١٠٠١٠١٫١٠١١١١٠١١

٢

= (١BD.A٤)

٦١

F

١

J

٠٣

WE

אא

()١٠٠١١٠٫١١٠٠١٠٠١٠١١

٢

אאא

K

א

W

١١٠١ ٠١٠١ ١٠٠٠

• ٠٠٠١ ٠١١٠

١

A B

• ٦

٨

∴()١٠٠١١٠٫١١٠٠١٠٠١٠١١

٢

= (١AB.٦٨)

٦١

١

J

١١

J

٦

אאאאא

Hexadecimal-to-Octal Conversion

אאאאאאאאא

אאאאאאא

אאא

W

F

١

J

١٣

WE

א

(AB٣E.٨٧D)

٦١

אא

K

א

W

אאא

א

W

(AB٣E.٨٧D)

٦١

= ()١٠١١١١١٠٠٠٠١٫٠١١١١١٠٠١١٠١٠١٠١

٢

אאאאא

W

٠١١ ١١١ ١٠٠ ١٠١ ٠١٠ ١٠٠

• ١٠١ ١١١ ١٠٠ ٠٠١

١

٢

٦ ٧ ٤ ٥

• ٥ ٧ ١ ٤

אא

K

∴(AB٣E.٨٧D)

٦١

= ()٥٧١٤٫٦٧٤٥٢١

٨

١

J

١١

J

٧

אאאאא

Octal-to-Hexadecimal Conversion

אאאא

،

א

،אאאא

אאאא

W

F

١

J

٢٣

WE

אא

()٢٤٣٫٥٢

٨

אאא

K

א

W

אא

W

∴()٢٤٣٫٥٢

٨

= ()٠١٠٠٠١١١٠٫١٠١٠١٠

٢

אאאאא

W

١٠١٠ ١٠٠٠

• ١٠٠٠ ١١١٠

١

٢

• ٧

١

אא

אאאא

K

∴()٢٤٣٫٥٢

٨

= ()١٧٫٢١

٦١

١

J

١١

J

٨

אאאאא

Arithmetic Operations in Hexadecimal System

אאאא

K

١

J

١١

J

٨

J

١

אא

אא

Hexadecimal Addition

אאאא

(٠,F)

אאאא

(F)

()٠١

אא،

()٠١

אאאאאאא

אאא

אאאא

K

א

אאאאאאא

אא

()٩

٦١

א

(A)

٦١

אא

()٩

٦١

(B)

٦١

א

(F)

٦١

K

אא

(F)

٦١

א

()٠١

٦١

אא

אאאאא

(F)

٦١

א

()١١

٦١

אאא

אאאאא

K

א

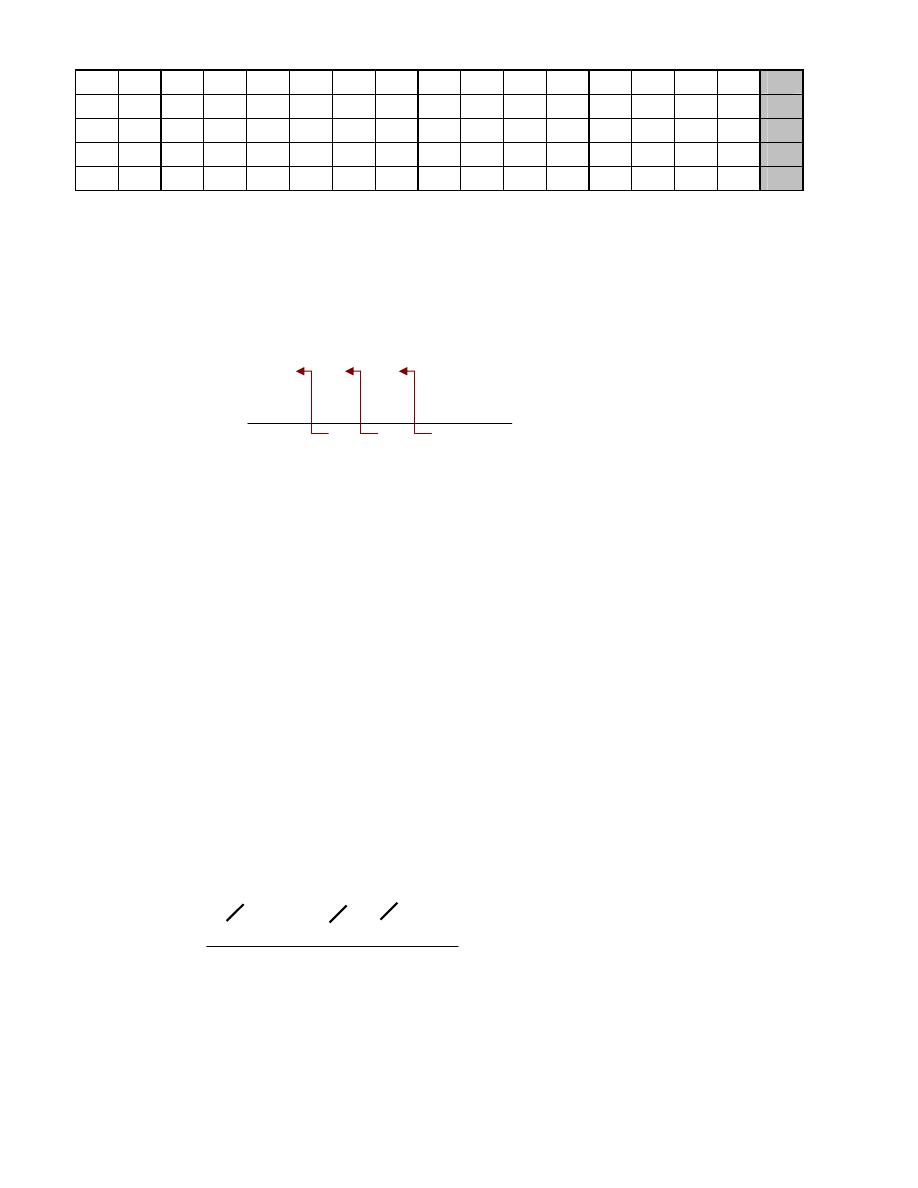

F

١

J

٤

E

א

،אאא

אאאאאאאאאא

אאאאא

K

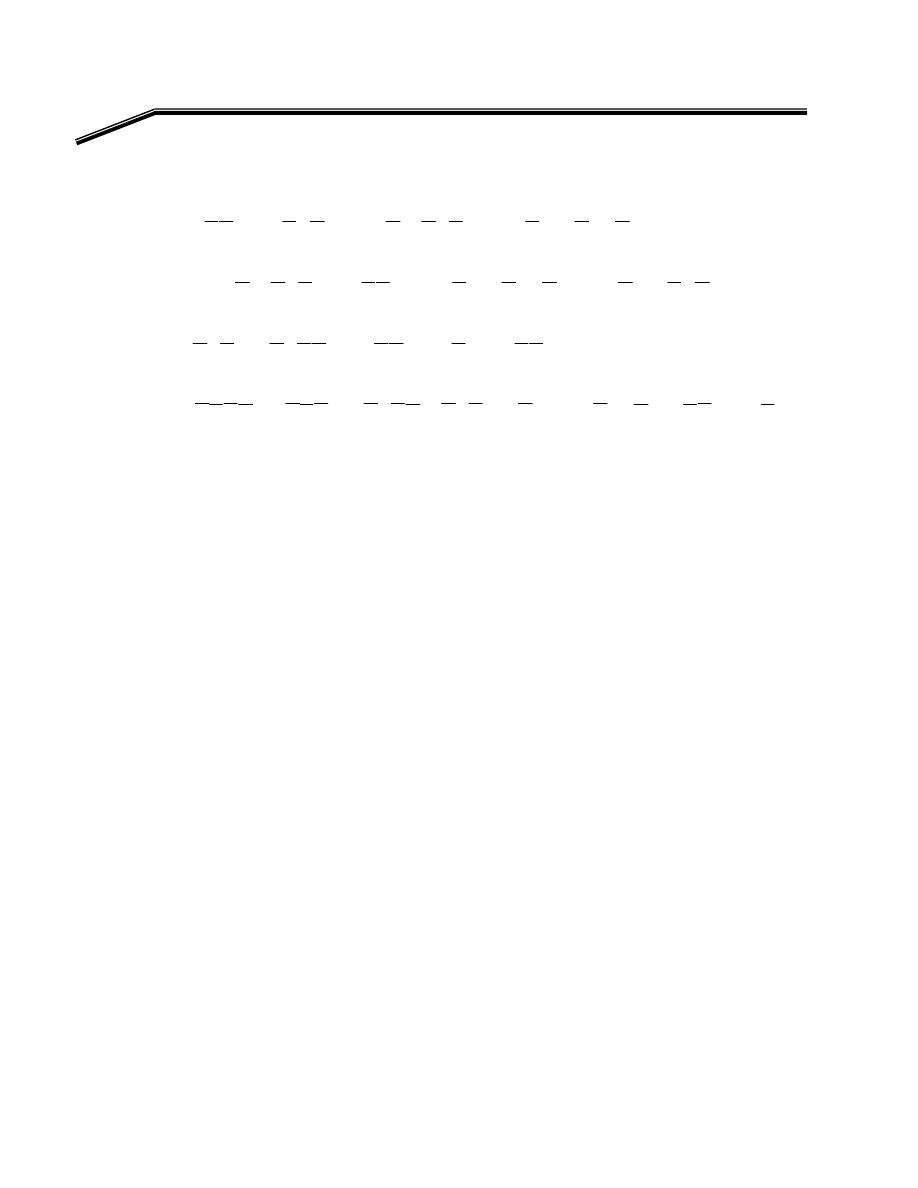

+

٠

١

٢

٣

٤

٥

٦

٧

٨

٩

A

B

C

D

E

F

٠

٠

١

٢

٣

٤

٥

٦

٧

٨

٩

A

B

C

D

E

F

١

١

٢

٣

٤

٥

٦

٧

٨

٩

A

B

C

D

E

F

٠١

٢

٢

٣

٤

٥

٦

٧

٨

٩

A

B

C

D

E

F

٠١

١١

٣

٣

٤

٥

٦

٧

٨

٩

A

B

C

D

E

F

٠١

١١

٢١

٤

٤

٥

٦

٧

٨

٩

A

B

C

D

E

F

٠١

١١

٢١

٣١

٥

٥

٦

٧

٨

٩

A

B

C

D

E

F

٠١

١١

٢١

٣١

٤١

٦

٦

٧

٨

٩

A

B

C

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٧

٧

٨

٩

A

B

C

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٨

٨

٩

A

B

C

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٩

٩

A

B

C

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٨١

A

A

B

C

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٨١

٩١

١

١

١

B

B

C

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٨١

٩١

١A

C

C

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٨١

٩١

١A

١B

D

D

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٨١

٩١

١A

١B

١C

E

E

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٨١

٩١

١A

١B

١C

١D

F

F

٠١

١١

٢١

٣١

٤١

٥١

٦١

٧١

٨١

٩١

١A

١B

١C

١D

١E

F

١

J

٤

E

אאאא

K

F

١

J

٣٣

WE

אא

W

(٥٣AB٢)

٦١

+ (١A٦٧٥)

٦١

א

W

אאאאאא

K

٣

٥A B ٢

+ ١A ٦

٧

٥

٥

٠

١

٢

٧

∴(٥٣AB٢)

٦١

+ (١A٦٧٥)

٦١

= ()٧٢١٠٥

٦١

١

J

١١

J

٨

J

٢

אאאא

Hexadecimal Subtraction

אאאאא

W

•

אאאאאאא

אאאאא

K

•

אא

א

()١

אאאאא

אאאאאאאא

אא

W

F

١

J

٤٣

WE

אא

W

(F٢ABD)

٦١

– (EF٤CE)

٦١

א

W

F

٢A B D

– E

F

٤C E

٣

٥E D

אאא

K

١

١

A

٩

١

E

١

E

אאאאאא

W

a)

٤٦b) ١١٢ c) ٢٥٧ d) ٢٧{٢٦

e)

٧٧{٠٦٢٥ f) ٤٧{٨٧٥ g) ٣٣{١٢٥

٢

E

אאאאאא

W

a)

١١٠١١b) ١١١٠١٠١ c) ١١١١١١ d) ١١١٠{١١

e)

١٠١٠١{١١٠١ f) ١١٠٠٠٠١{١١٠١١

٣

E

אאאא

W

a)

٠٠١+ ١١١

b)

٠١١١{١١ + ١١{١٠

c)

١١١١+ ١١٠١

d)

١٠٠١{١٠١ + ١١٠١{١١

٤

E

אאאאא

W

a)

١٠١١– ٠١٠٠

b)

١٠٠١– ٠١١١

c)

٠١٠١١– ١٠١١١

d)

٠٠١١– ١٠٠١

٥

E

אאאאאא

W

a)

١٠١٠١١٠٠

b)

٠٠١٠٠١١١

c)

١٠١٠١٠٠٠

٦

E

אאאאאא

W

a)

٠١١٠١١١١

b)

١٠١١١٠١٠

c)

١١٠٠١١٠٠

٧

E

א

אאא

אאאאאאא

אא

(

٨-bits)

W

a)

H ٨٢

b) –

٣٨c)

H ٩٩

d) –

٠٢١

٨

E

א

אאאאאאאאא

אא

(

٨-bits)

W

a)

H ٤١

b) –

٣٦c)

H ٧٠١d)

–

٢٢١

٩

E

אא

F

٨

E

אאאא

K

٠١

E

אאאאאאאאא

אא

W

a)

١٠٠٠١١١٠١

b)

٠٠١٠٠١١٠

c)

١١٠٠١١٠١

١١

E

אאאאאאאאאאא

W

a)

١٠١١١٠٠١

b)

٠١١٠٠١١٠

c)

١٠١١٠١٠١

٢١

E

אאאאאאאאאאא

W

a)

١١٠١٠١٠١

b)

١٠١١١١٠٠٠

c)

١١٠١١١٠١

٤١

E

אאאאא

W

a)

٠١١٠١٠٠٠– ٠٠١١٠٠١١

b)

٠٠٠٠١١١٠– ١٠١٠١١١١

c)

٠٠١١٠٠٠١– ٠٠١١١٠٠١

d)

١٠٠١١٠١١– ١١١٠٠١١١

٥١

E

אאאאאאא

W

a)

٠٥

b)

٠٠١

c)

١٩٣٦

d)

٧٧{٣٧٥

e)

٠٢١{٥١٥٦٢٥ f) ١٤٤{٥٦٢٥ g) ٩١٥{١٤١

٦١

E

אאאאאאא

W

a)

٢٤

b)

٤٥٢

c)

٧٥٠١

d)

٧٣{٥

e)

٦٩{١١

f)

٥١١{٣

g)

٧٦٣٤١{١٢

٧١

E

א

אאאאאא

W

a)

٢٧

b)

٣١١

c)

٦١{٣ d)

٧٣{٦

e)

٢٢١{٧٧٥

f)

٧١٤{٦٣٢

g)

٦٧٢{٦٢١

٨١

E

אאאאאאא

W

a)

١٠١٠١١{١١٠١ b)

٠٠١٠١١١١{١١٠١٠١

c)

١١١٠١١٠١١{١٠١٠١

d)

١١٠١٠٠١٠٠٠١{١٠٠١ e)

١١١٠١٠١{١١١٠١

٩١

E

אאאא

W

a) (

)٥١

٨

+ (

)٧١

٨

b) (

)٤٤

٨

+ (

)٦٦

٨

c) (

)٣٢١

٨

+ (

)١٢٣

٨

d) (

)٢٧٢

٨

+ (

)٦٥٤

٨

٠٢

E

אאאא

W

a) (

)٢٣

٨

– (

)٥٢

٨

b) (

)٧٤١

٨

– (

)٤٧

٨

c) (

)٥١٣

٨

– (

)٢٢٢

٨

d) (

)٧٣٤

٨

– (

)٠٤٣

٨

١٢

E

אאאאאאאא

W

a)

٤١

b)

٠٨

c)

٠٦٥

d)

٠٠٠٣

e)

٠٠٥٢٦f)

٤٠٢{١٢٥ g) ٢٥٥{٨٧٥ h)

١٣٦{٢٥

٢٢

E

אאאאאא

א

W

a)

٩F

b) D

٢٥

c)

٧٦F

d) ABCD

e) F.

٤

f) B

.٣E

g)

١١١١{١ h)

٨٨٨{٨

٣٢

E

אאאאאאאאא

W

a)

٨

b)

١C

c) A

٤٦d) ١F.C e)

٩٣٢{٤

٤٢

E

אאאאא

אאא

W

a)

١٠٠١{١١١١

b)

٠٠٠٠١{١

c)

١٠١٠١١{١١٠٠١

d)

١١١٠٠١٠١{١١١٠١١ e) ١٠٠٠٠٠٠{٠٠٠١١١

f)

٠٠١١١١١{١٠٠٠٠١١

٥٢

E

אאאאאא

W

a)

٣١A

b)

٥٢E٦

c)

٦١٠٣

d) B

.٤C

e)

.٨٧D٣

f)

.٩٥٦٢F٤١

٦٢

E

אאאאאא

W

a)

٧٣

b)

٥٢٧c) ٢٤٧٦{٢

d)

٧١١١{١٦

e)

٠٠٦١{٥٢٤

f)

٠٠٠٣{٦١٢٥

٧٢

E

אאאא

W

a) (

)١٤

٦١

+ (

)٦٣

٦١

b) (C

)٨

٦١

+ (

٣A)

٦١

c) (

٩B)

٦١

+ (

)٥٦

٦١

d) (

١١D)

٦١

+ (

٢E١)

٦١

f) (

٧٧CB٥)

٦١

+ (A

٥F٧٢)

٦١

g) (

٣١EFD)

٦١

+ (

١٢BB٣)

٦١

-

١

-

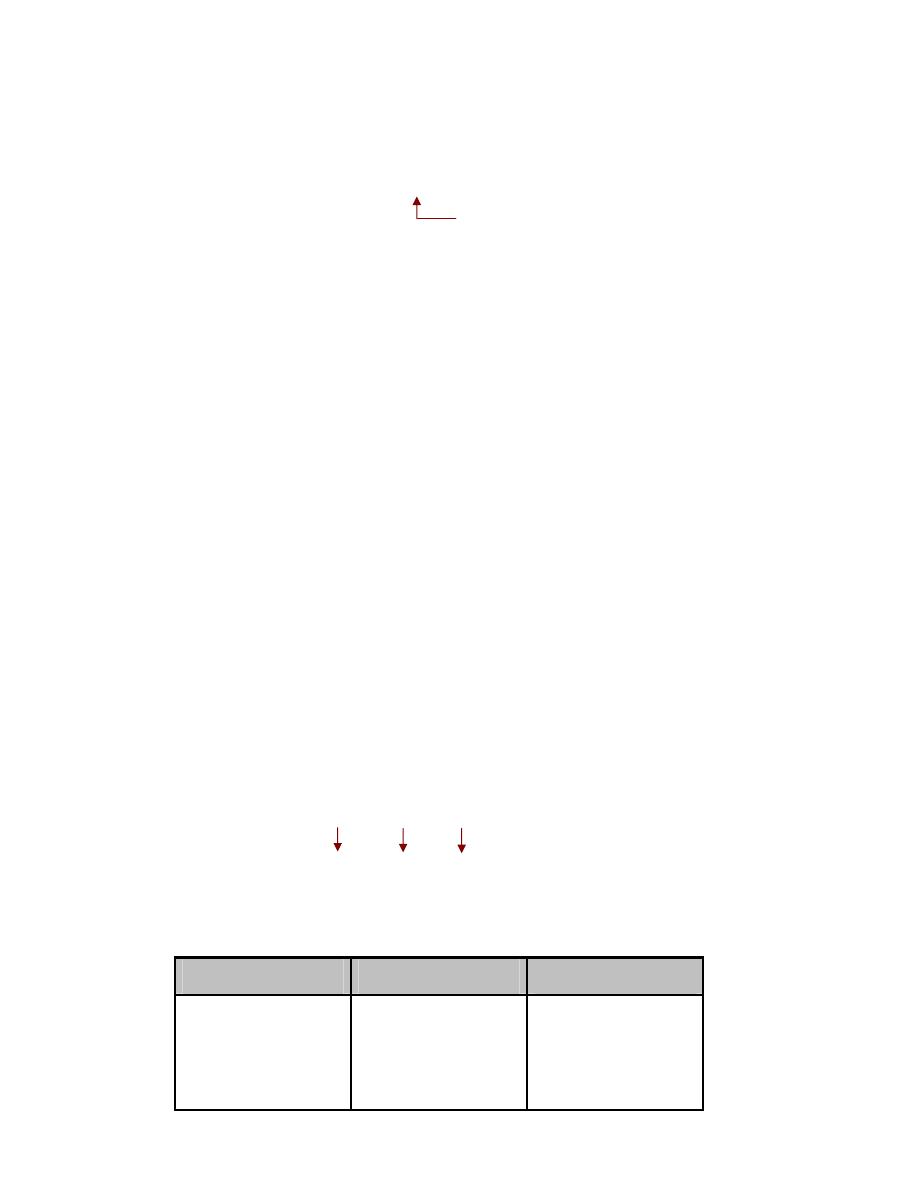

אאאא

אאאא

א

א

אאא

ã¹]<gè…‚jÖ]æ<ËÖ]<Üé×Ãj×Ö<íÚ^ÃÖ]<퉉ö¹]

אאאא

אא

אא

٢

אא

٧٤١

א

א

אאאא

א

-

٥٣

-

אאא

אא

W

•

אאאאא

K

•

אאאאא

K

•

אאאא

K

•

אאאאא

K

•

אאאאא

K

•

אאאא

K

•

אאאאא

K

•

אאאאאאא

K

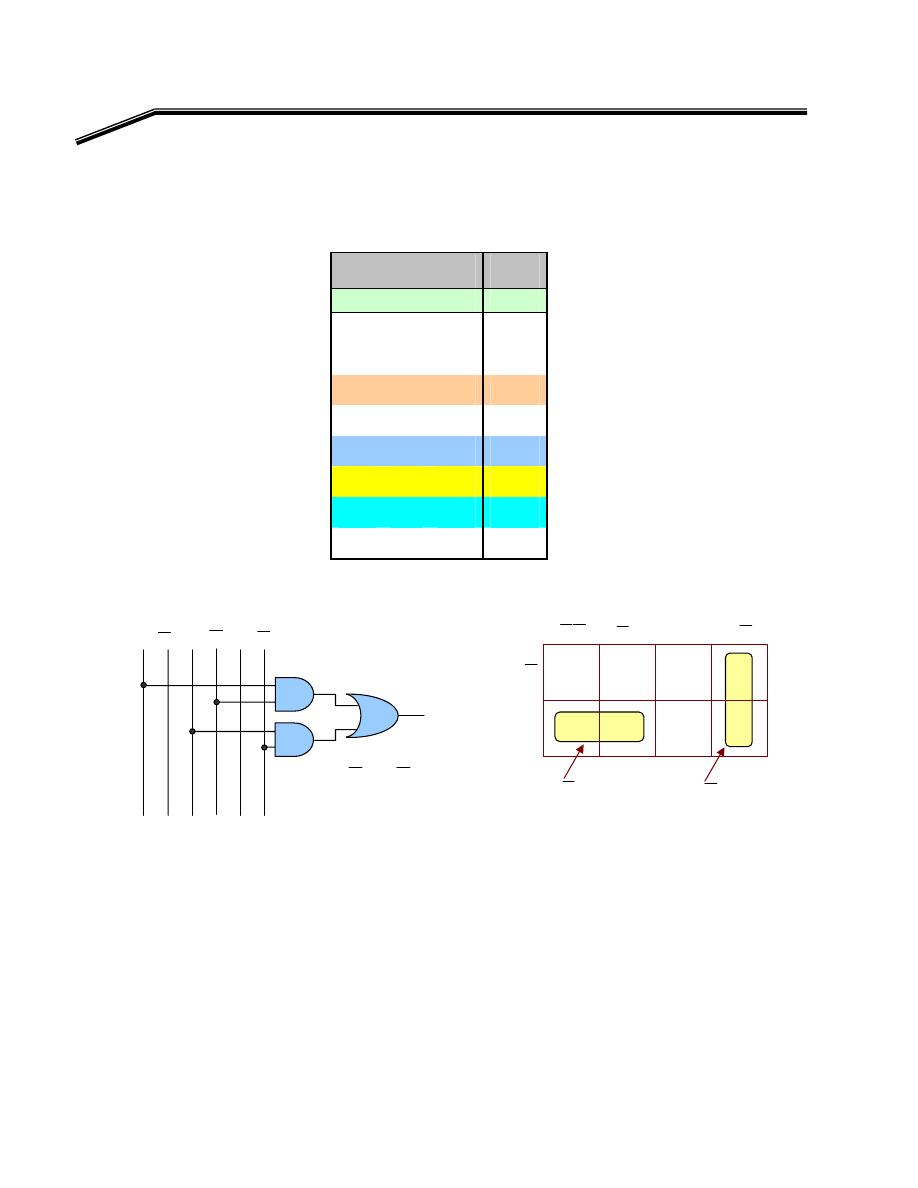

אא

٧٤١

א

א

אאאא

א

-

٦٣

-

٢

J

١

Introduction

א

אא

J

א

J

א

J

א

J

،אא

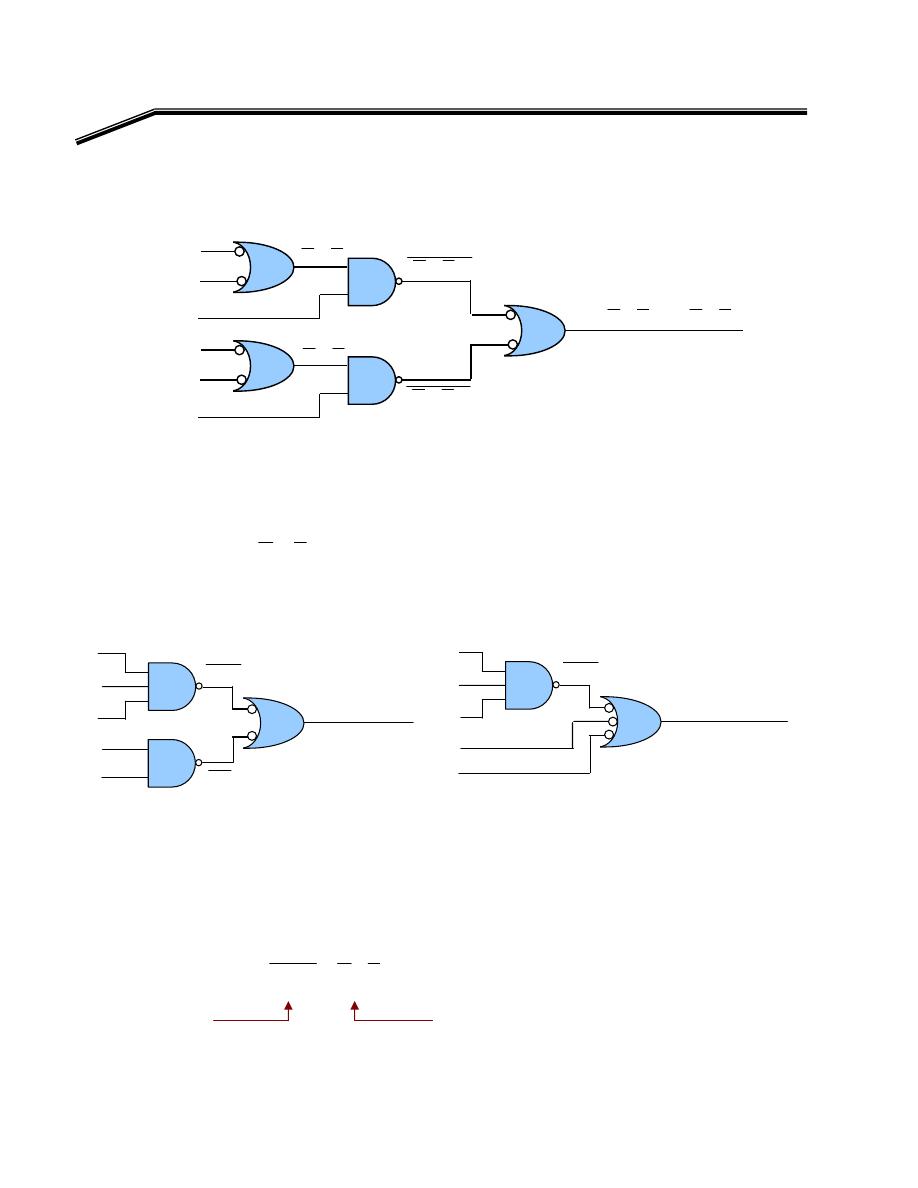

אאאא

א

אאאא،אאאא

אאאאאא،אא

אאא

K

،אאאאא

?

אא

?

א

אאאאא

אא

K

א

אאאאאאא

אא

AND

א،

OR

א،

NOT

א

(INVERTER)

K

א

،אאאאאאאאא

א

אאא

K

٢

J

٢

אא

Logic Signal Levels

אאאאאא

אא،אא

K

אאאא

א

،،

،א

אאא

אא،א

אאא

J

א

א

(HIGH)

א

(

)١

א،א

(LOW)

א

(

)٠

אא،א

(

)١

א

א

(TRUE)

،

אא

(

)٠

אאא

(FALSE)

K

א،א

(Positive Logic)

،

א

א

(Negative Logic)

K

אאאאא

(

)١

א

אא

(

)٠

אא،אא،א

(

)٠

א

אא

(

)١

אאא

K

אא

٧٤١

א

א

אאאא

א

-

٧٣

-

٢

J

٣

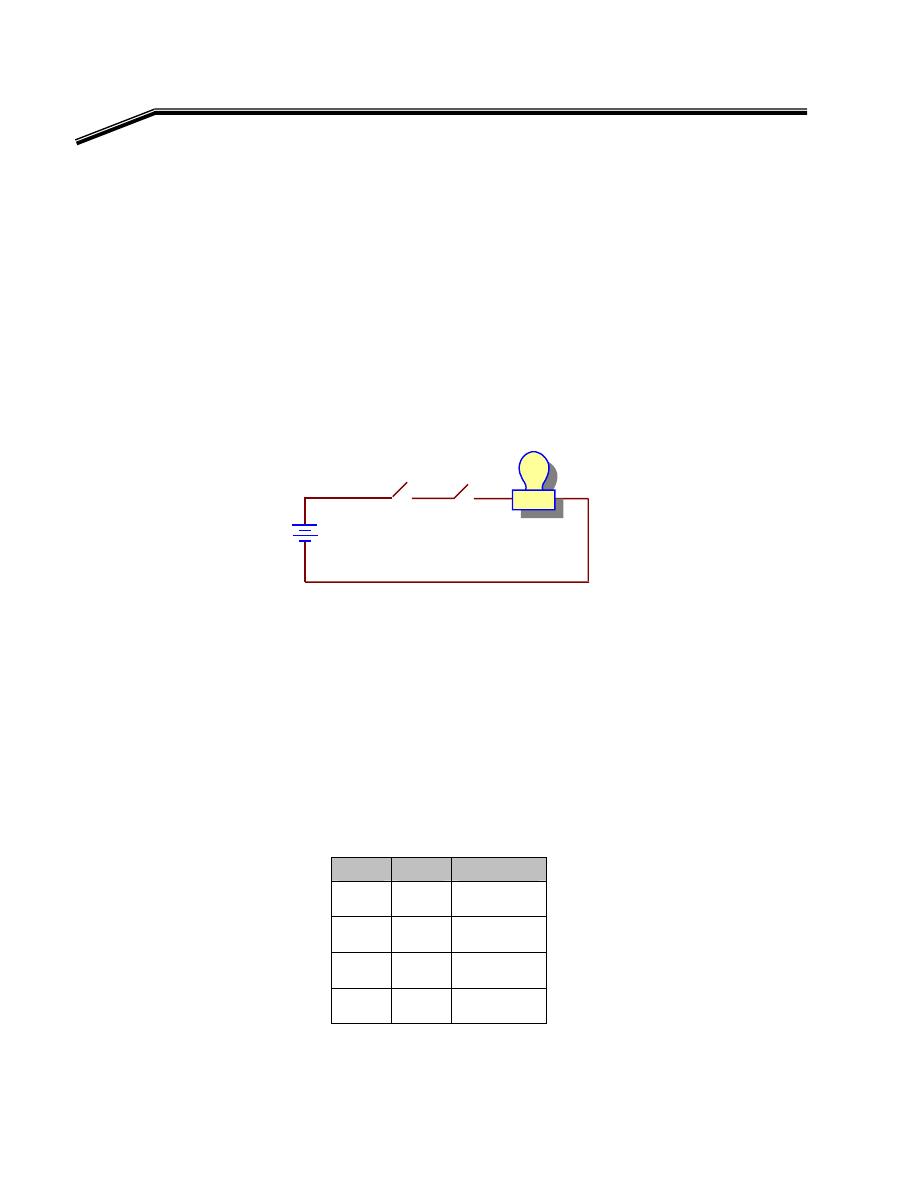

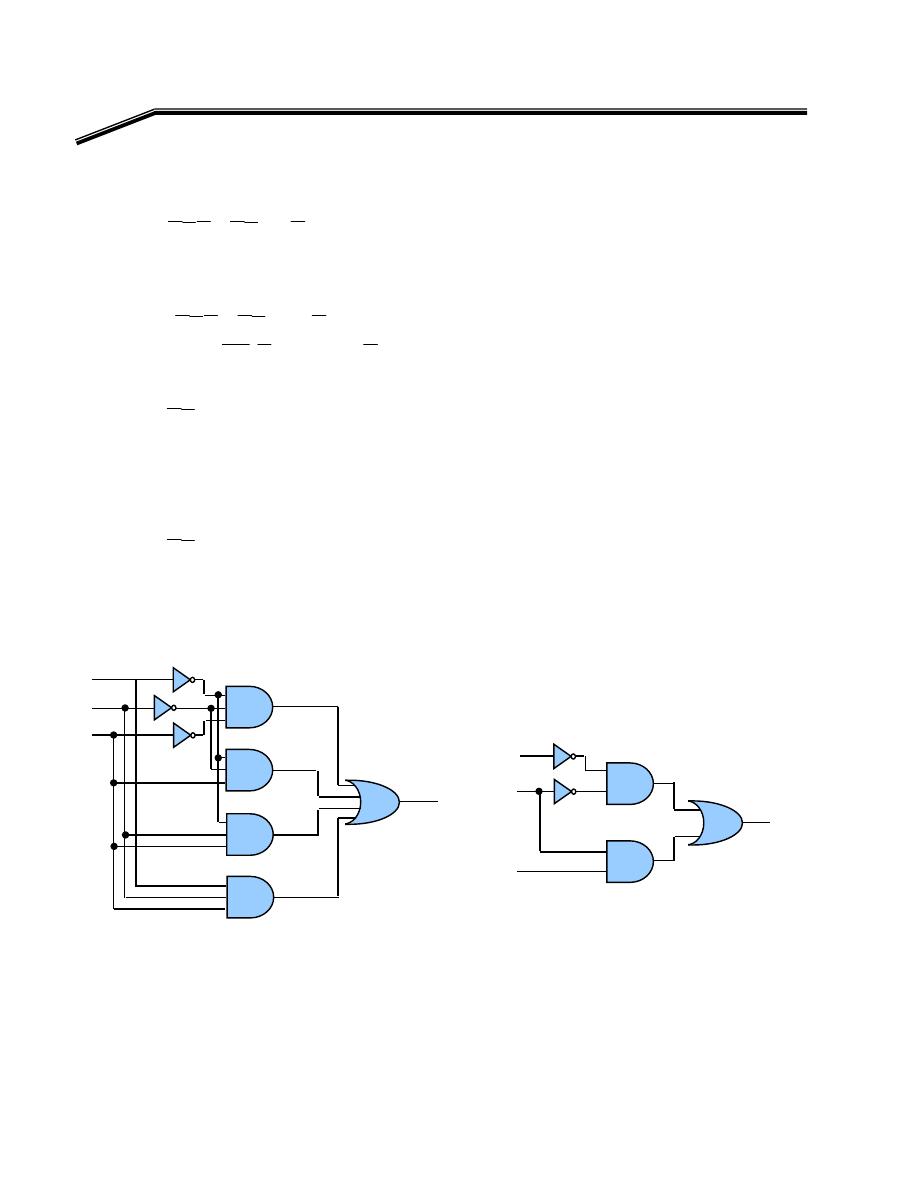

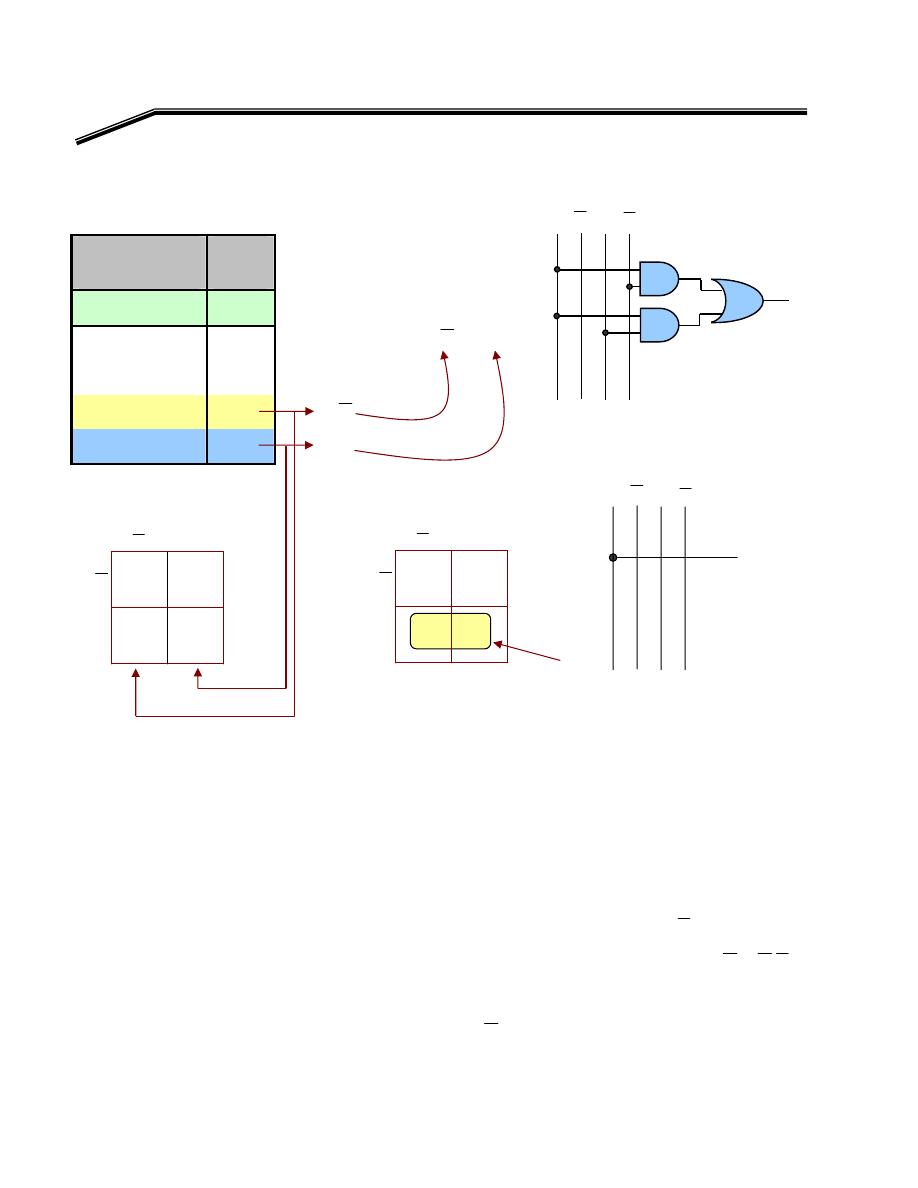

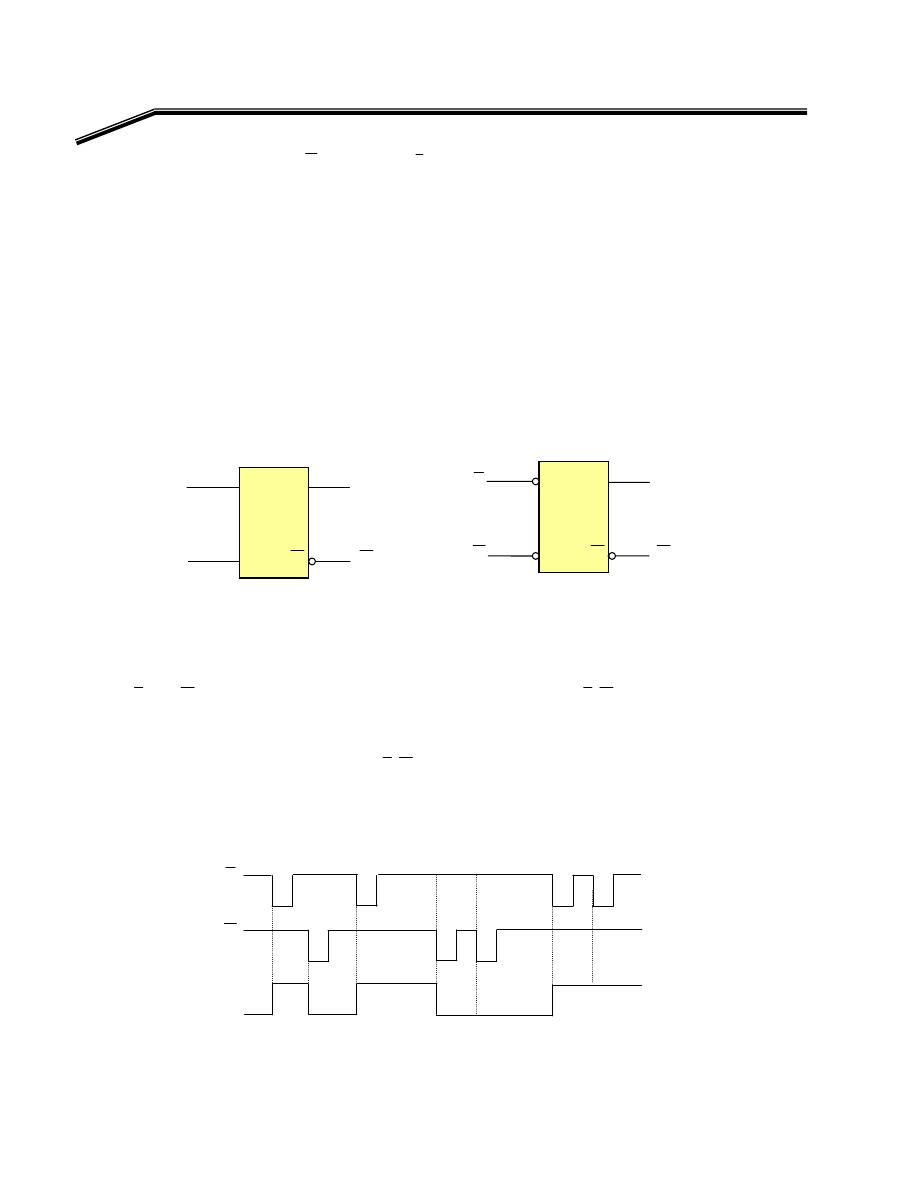

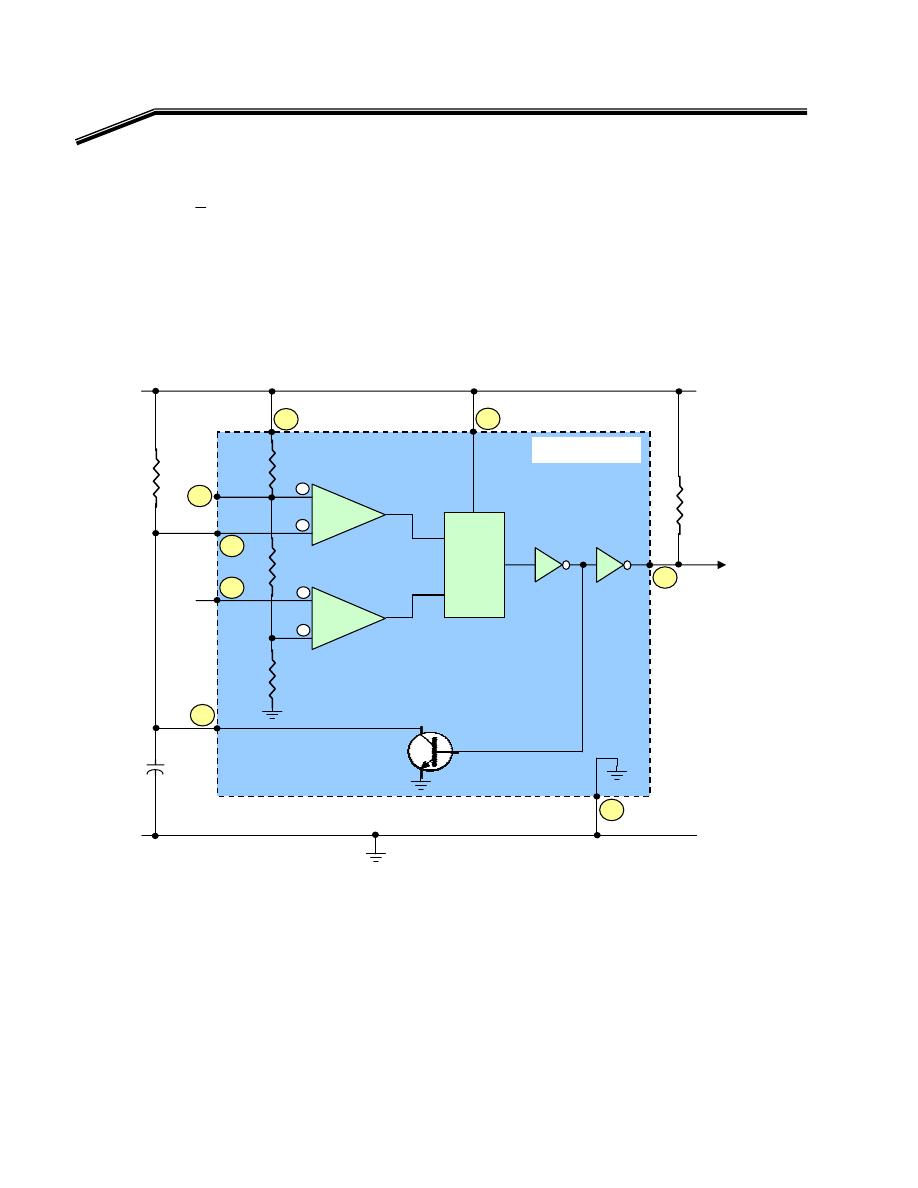

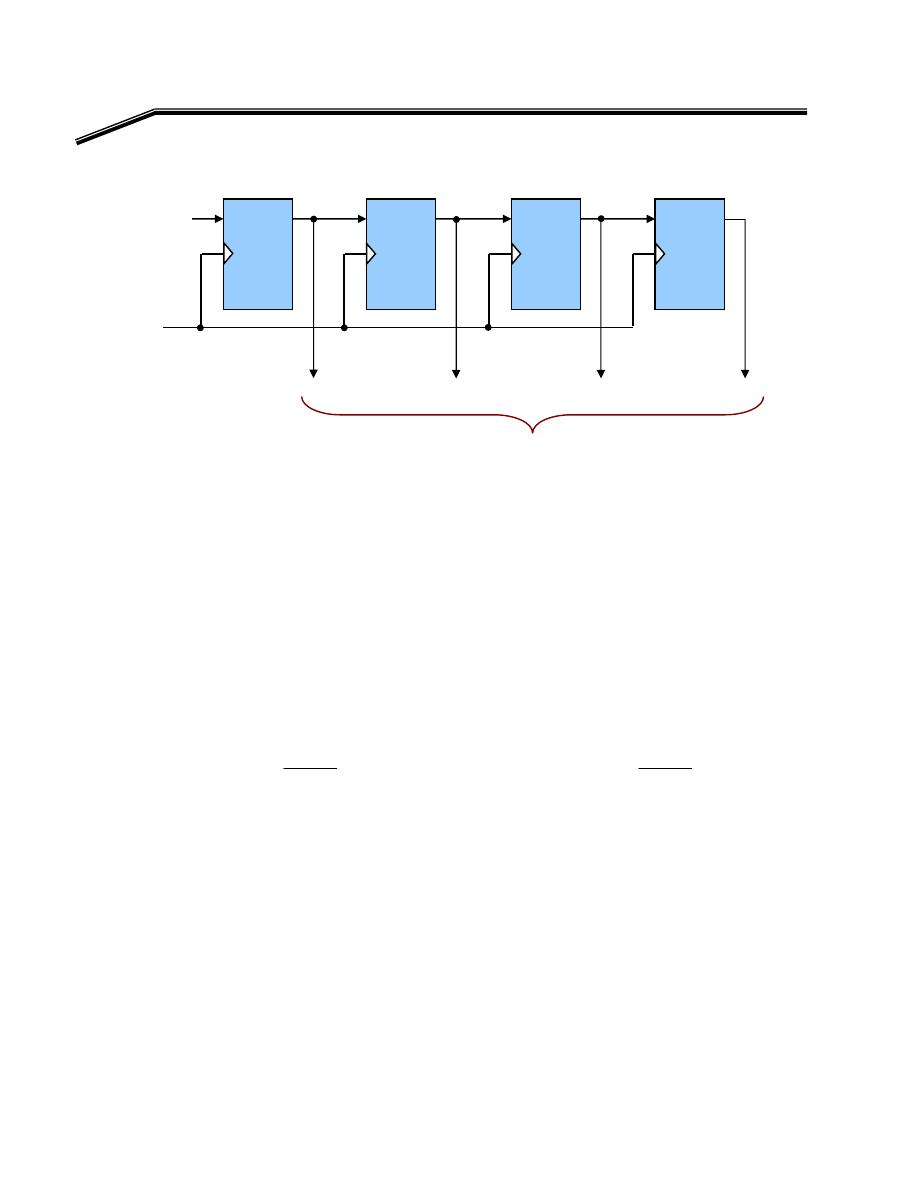

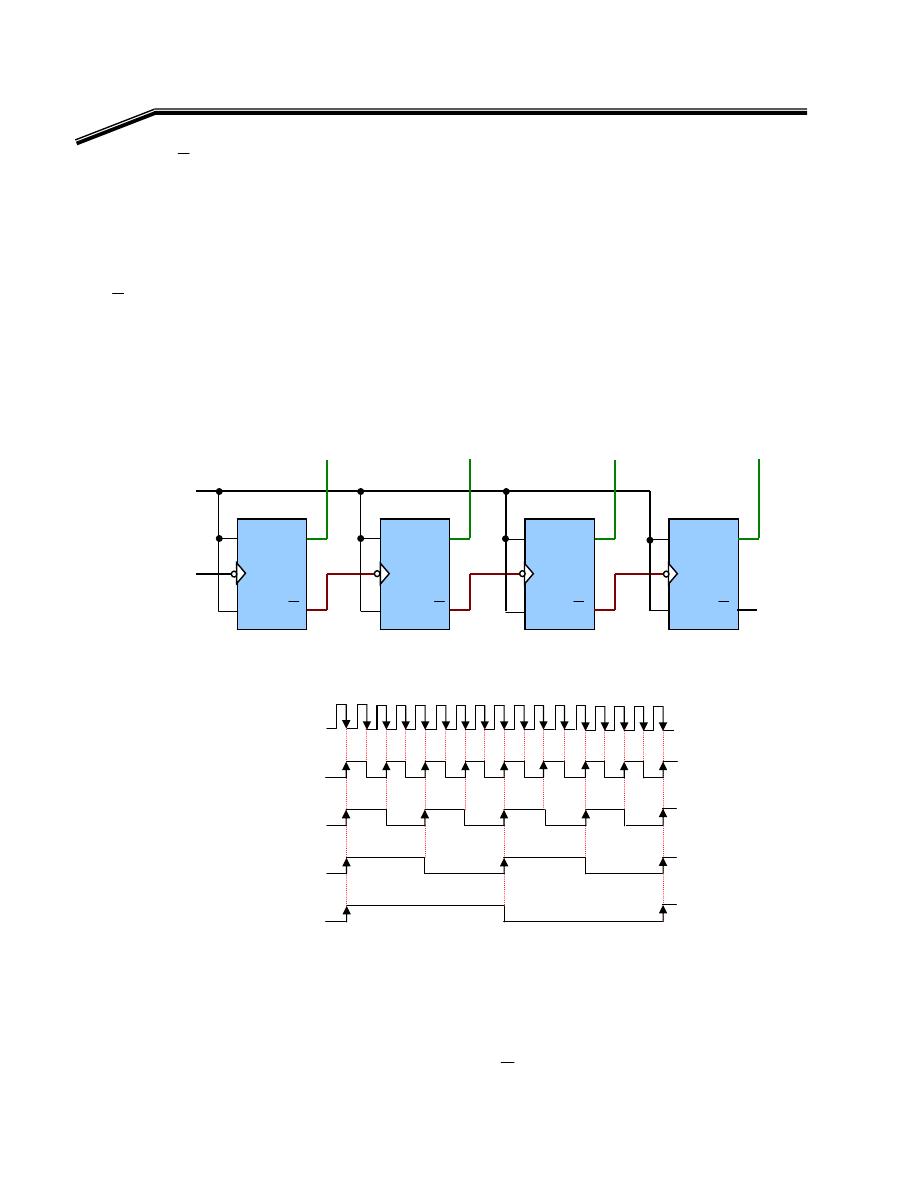

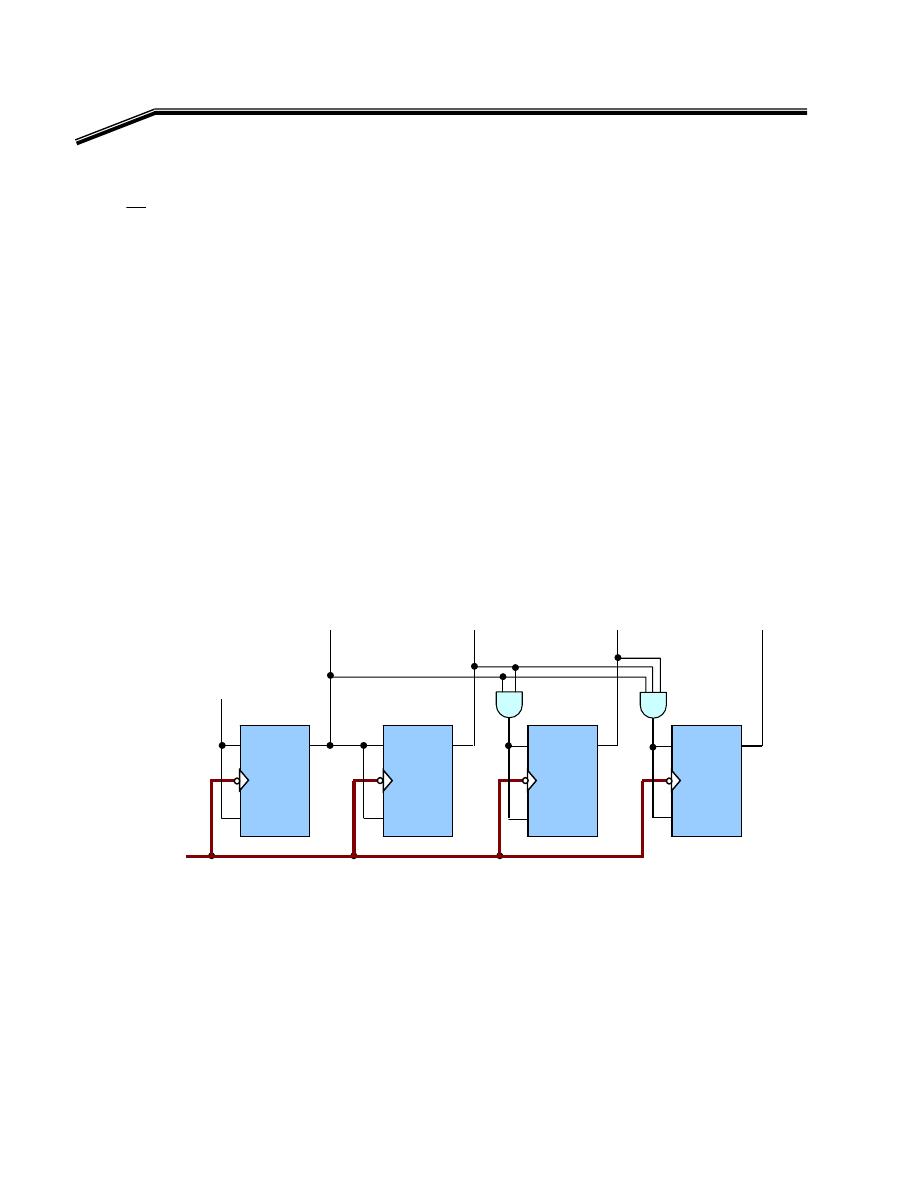

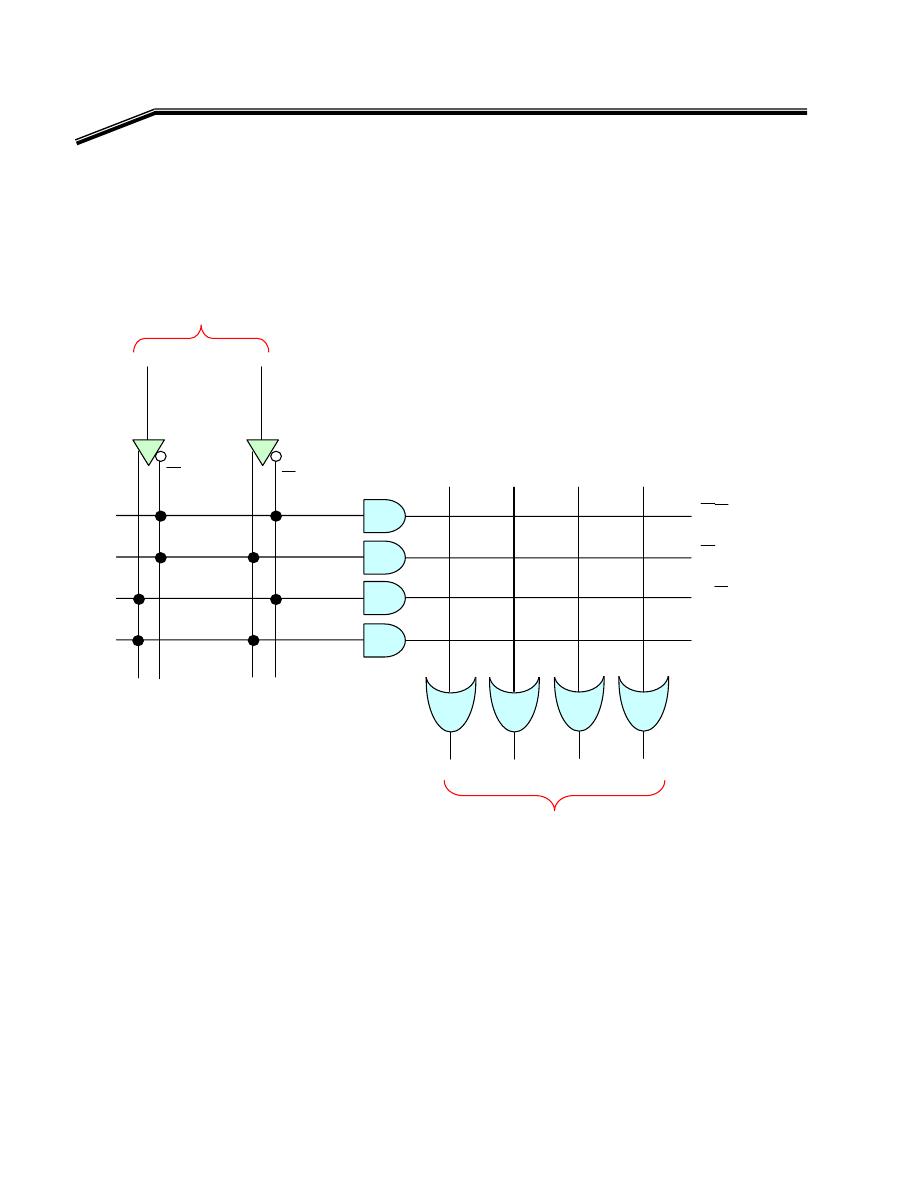

א

AND

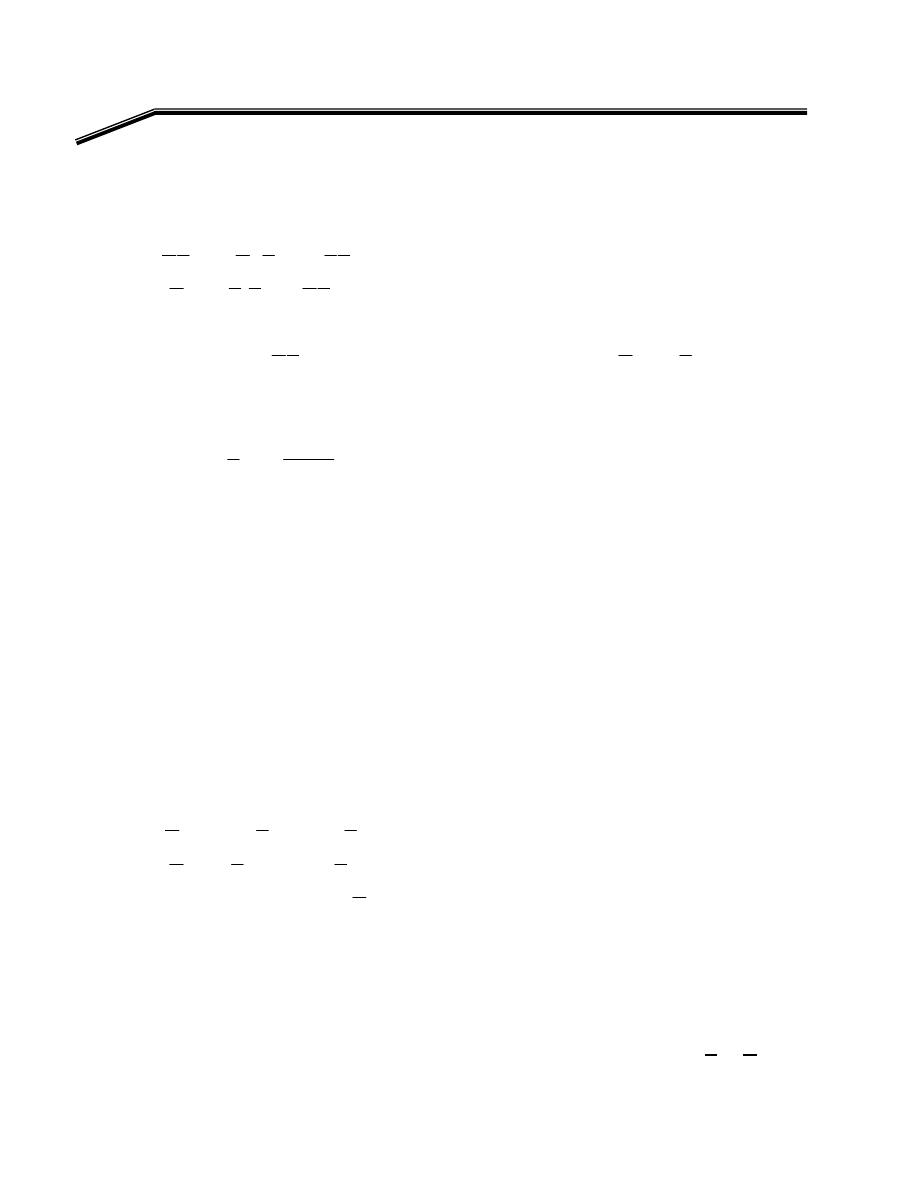

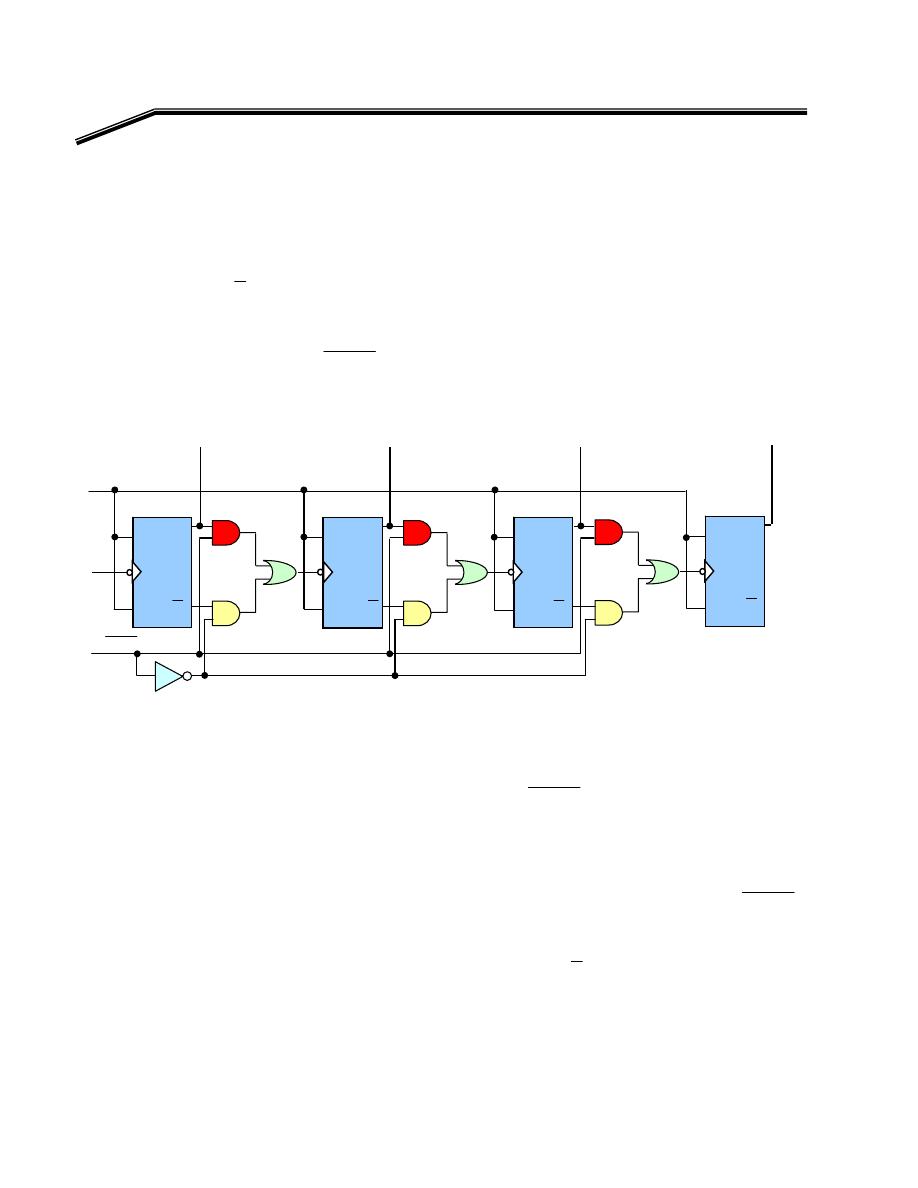

AND Gate

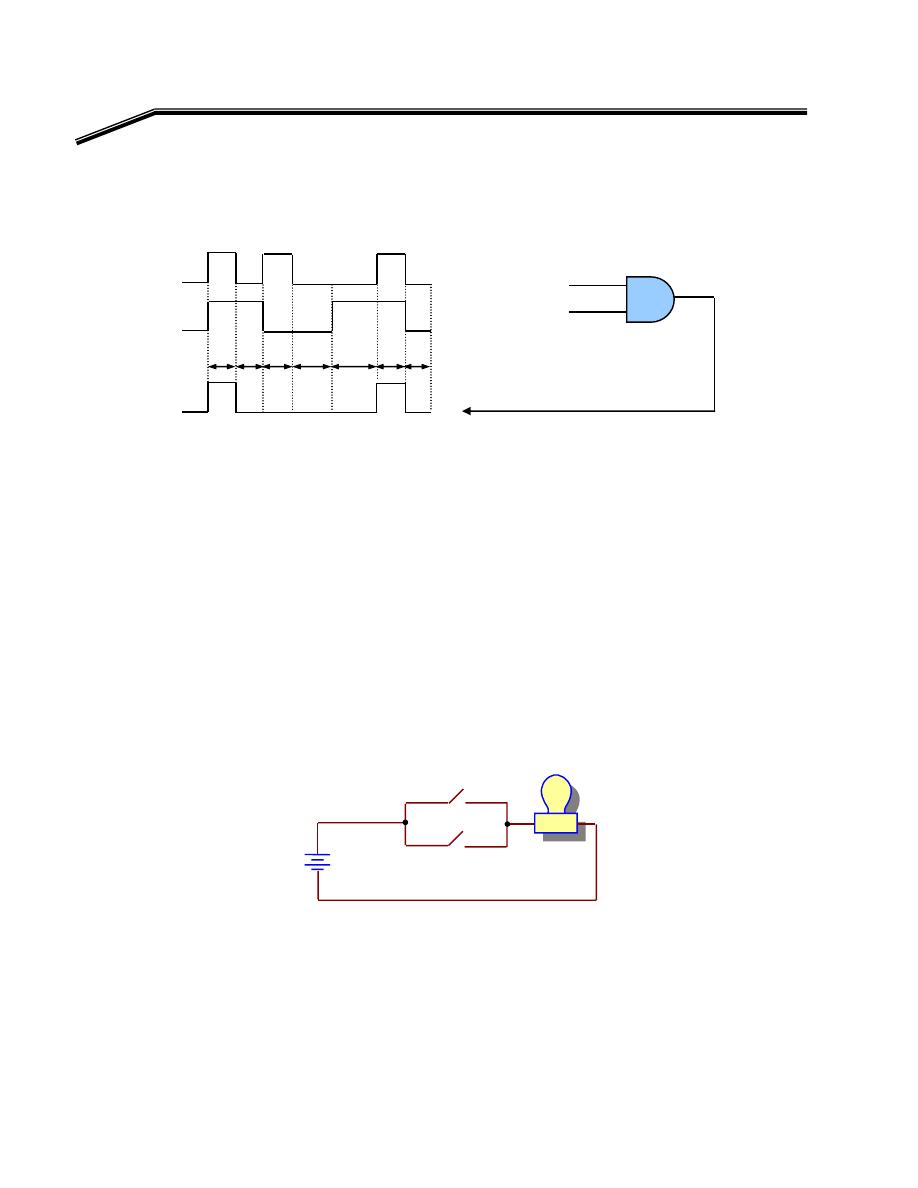

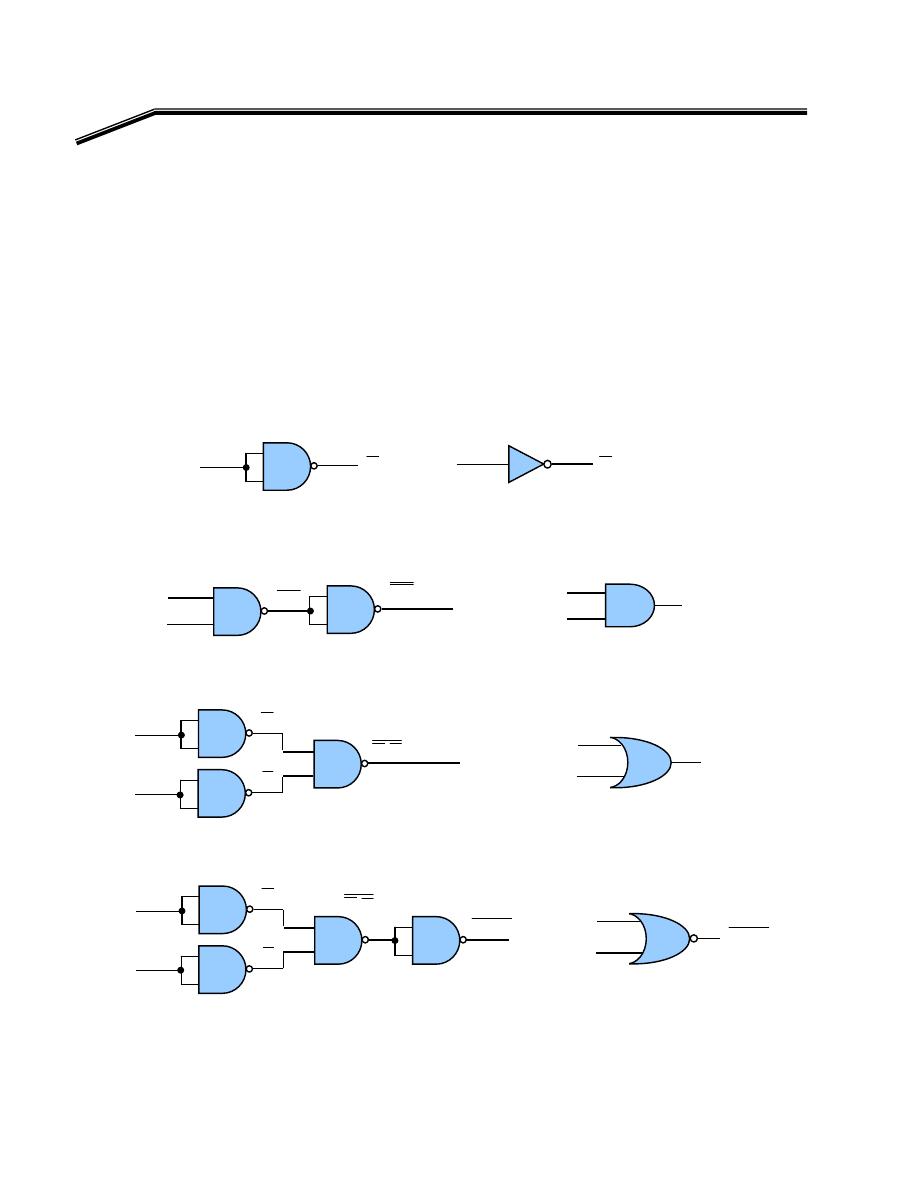

אא

AND

אאאאא

אאא

(Logic Functions)

K

אא

AND

אא،א

א

(Logical Multiplication)

،

אאאא

אאא

א

F

٢

J

١

E

،

א

A

,

B

א

אאא

(Two Binary Variables)

(

)٠

א

א

(Open)

(

)١

אא

(Closed)

K

F

٢

J

١

E

אא

AND

אא

K

א

"

L

"

אאא

(

)١

א

(ON)

(

)٠

א

(OFF)

K

אא

،

،א

F

٢

J

١

E

אא

א

(L)

א

K

אא

(L)

אאאא،א

(Truth Table)

K

L

B

A

F

٢

J

١

E

אא

F

٢

J

١

KE

Voltage Source

(A)

(L)

(B)

אא

٧٤١

א

א

אאאא

א

-

٨٣

-

א

F

٢

J

٢

E

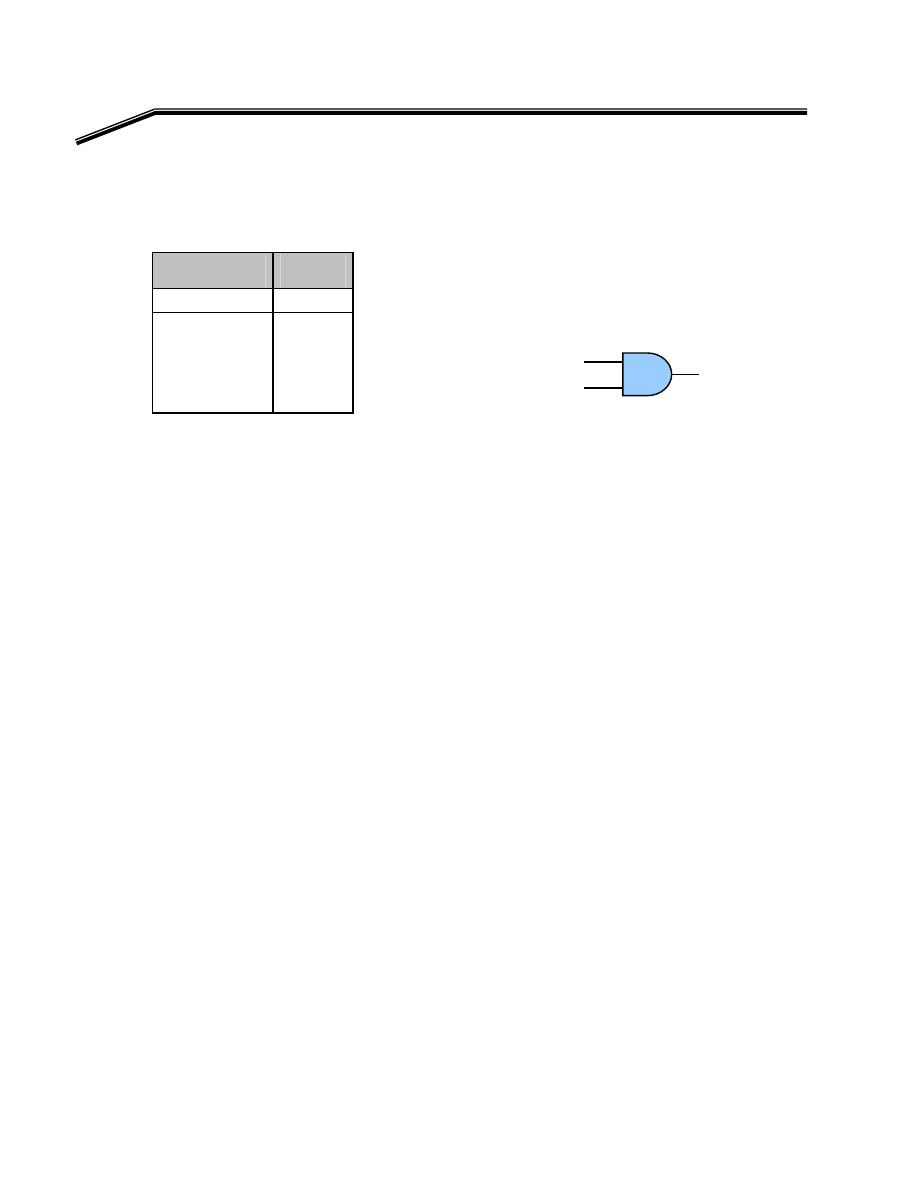

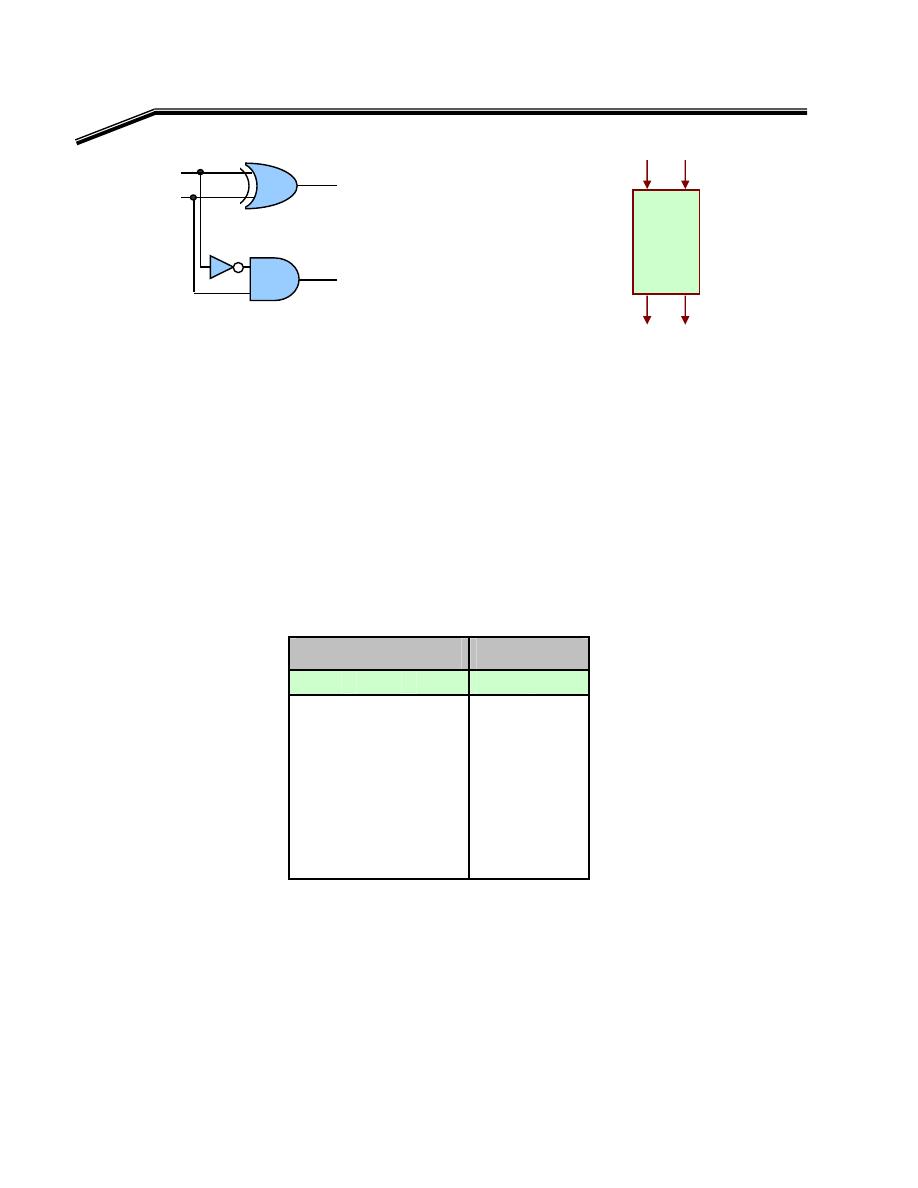

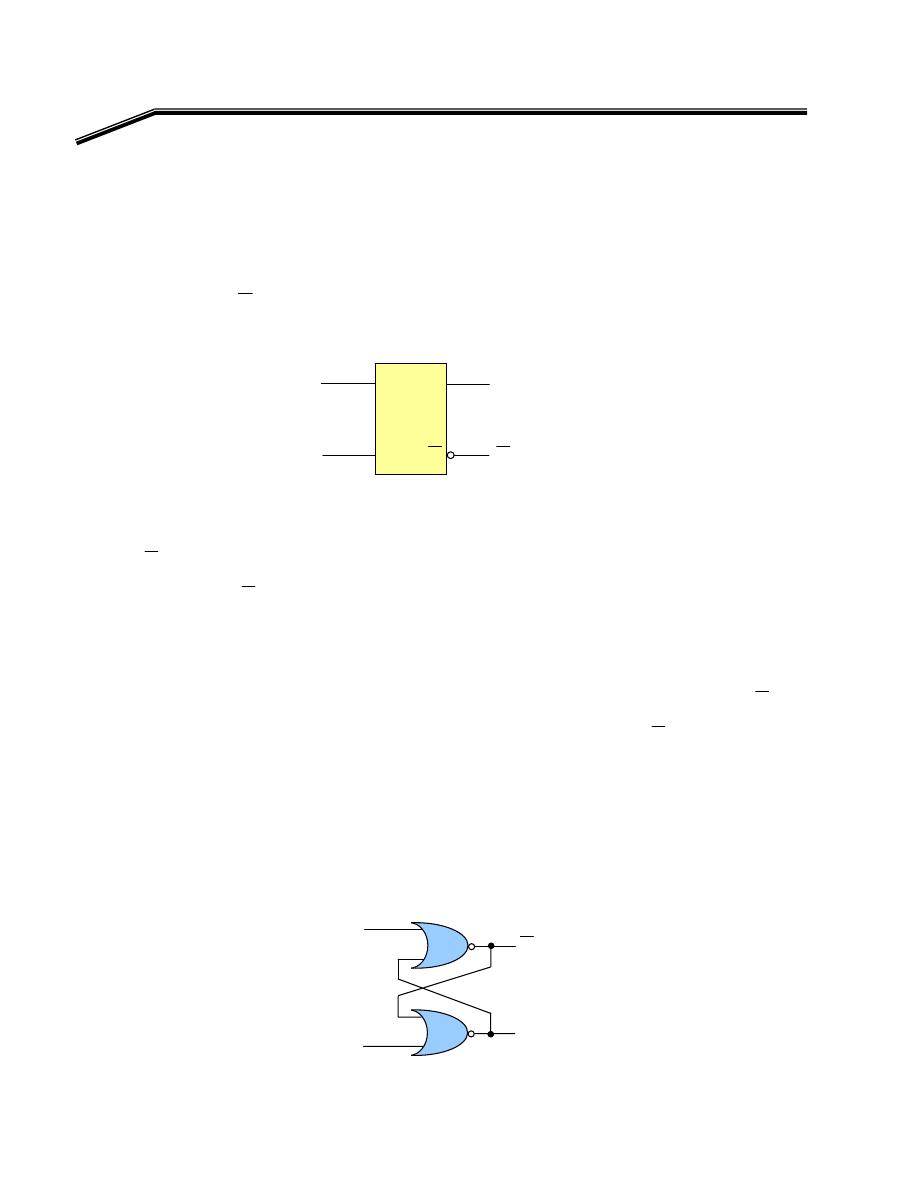

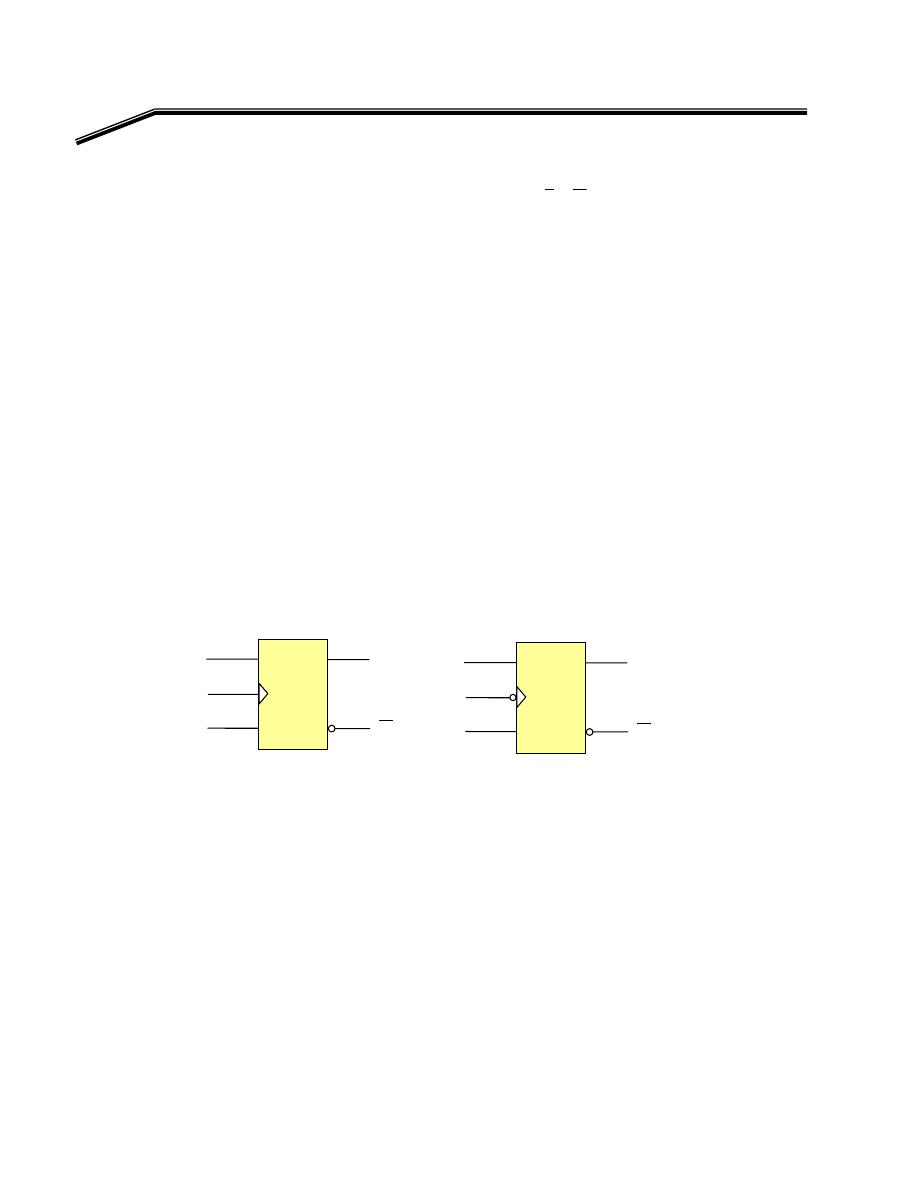

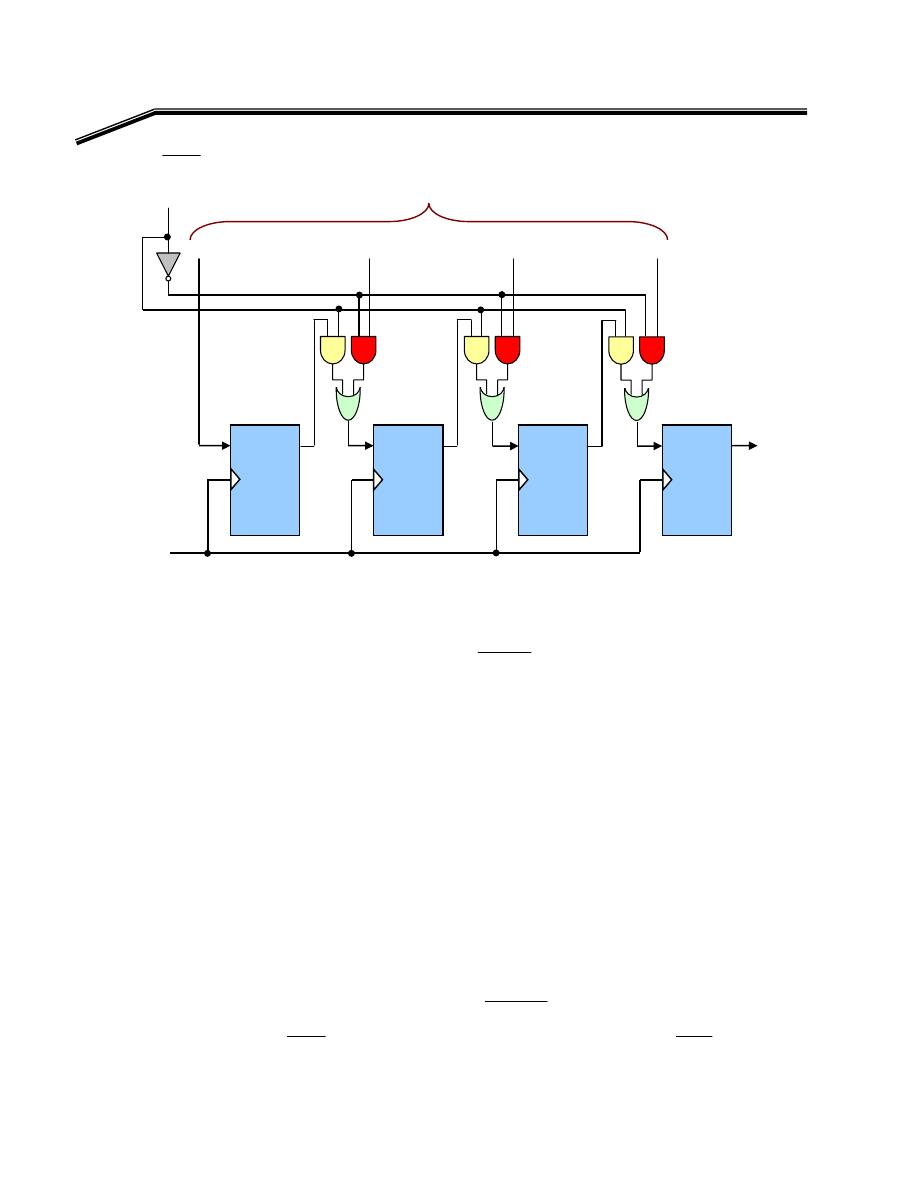

אאא

(Standard)

א

AND

א،

A

,

B

א

Y

אא،

AND

K

א

F

٢

J

٢

E

אא

AND

K

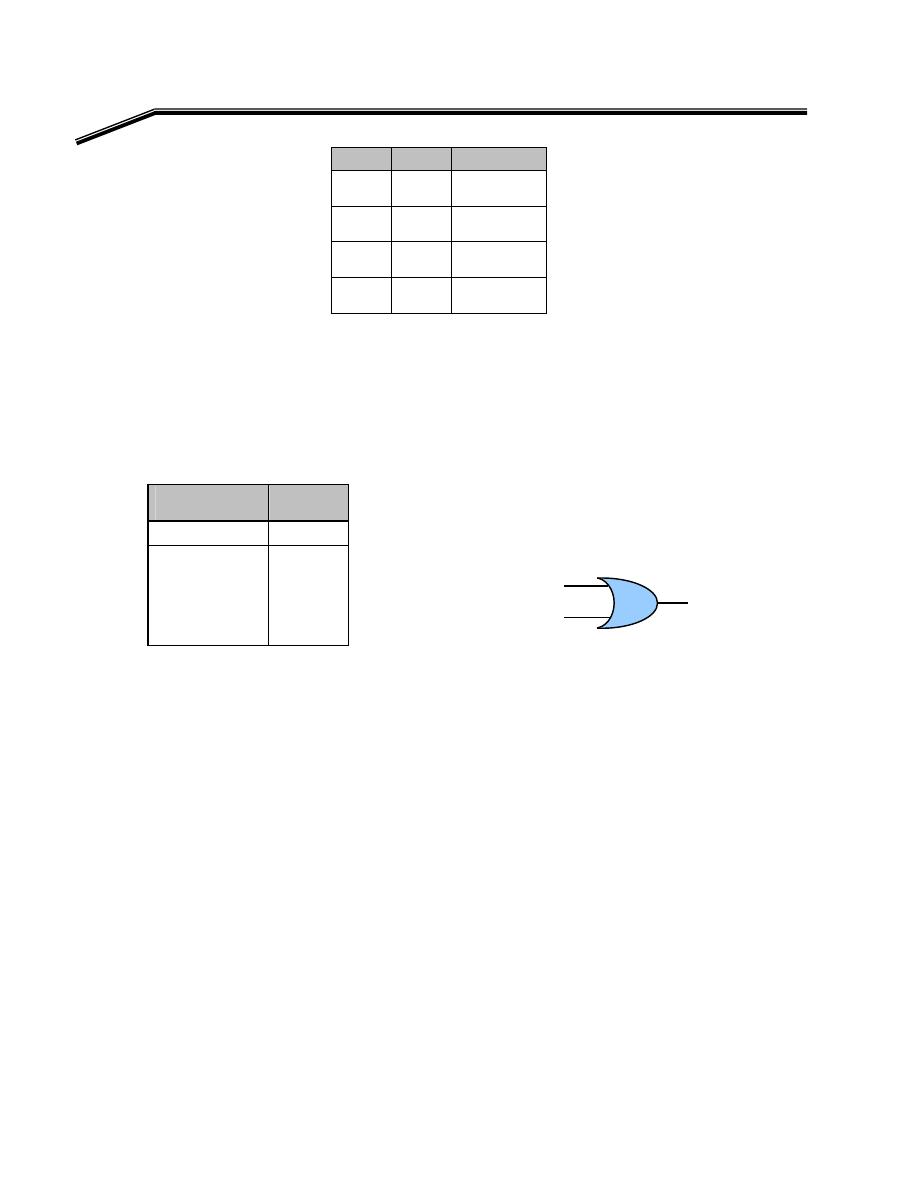

א

א

Y

B

A

٠

٠

٠

٠

١

٠

٠

٠

١

١

١

١

F

٢

J

٢

E

אא

AND

K

F

٢

J

٢

E

אא

AND

K

א

(bits)

،

א

(

)١

א

א

A

,

B

(

)١

،א

א

AND

،אא

א

(

)١

א

(

)١

K

אא

J

אאא

א

W

n

2

N

=

W

N

אא

n

אא

K

W

אא

4

2

N

2

=

=

אא

8

2

N

3

=

=

אא

16

2

N

4

=

=

F

٢

J

١

EW

•

אאא

AND

K

•

אא

AND

؟

א

W

א

AND

،אא

F

٢

J

٣

E

א

אא

K

Y

B

A

אא

٧٤١

א

א

אאאא

א

-

٩٣

-

א

א

Y

C

B

A

٠

٠

٠

٠

٠

١

٠

٠

٠

٠

١

٠

٠

١

١

٠

٠

٠

٠

١

٠

١

٠

١

٠

٠

١

١

١

١

١

١

F

٢

J

٣

E

אא

AND

K

•

אאא

W

32

2

2

N

5

n

=

=

=

אא

(Boolean Algebra)

אאאא

אא،א

(Boolean Expression)

אא

K

אאא

AND

א

W

B

A

Y

•

=

א

W

א

Y

A AND B

F

•

AND

E

א،

אא

W

Y = AB

א

Y

A AND B

K

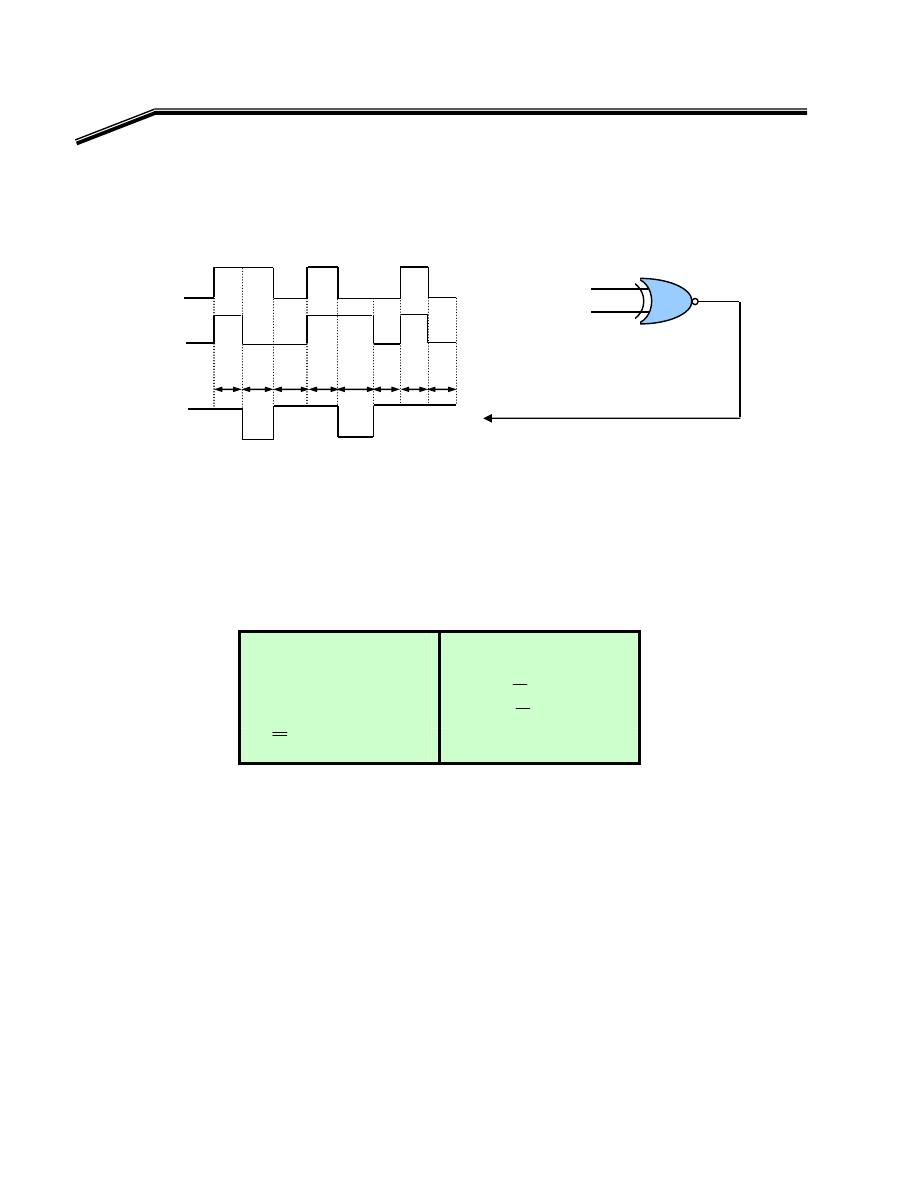

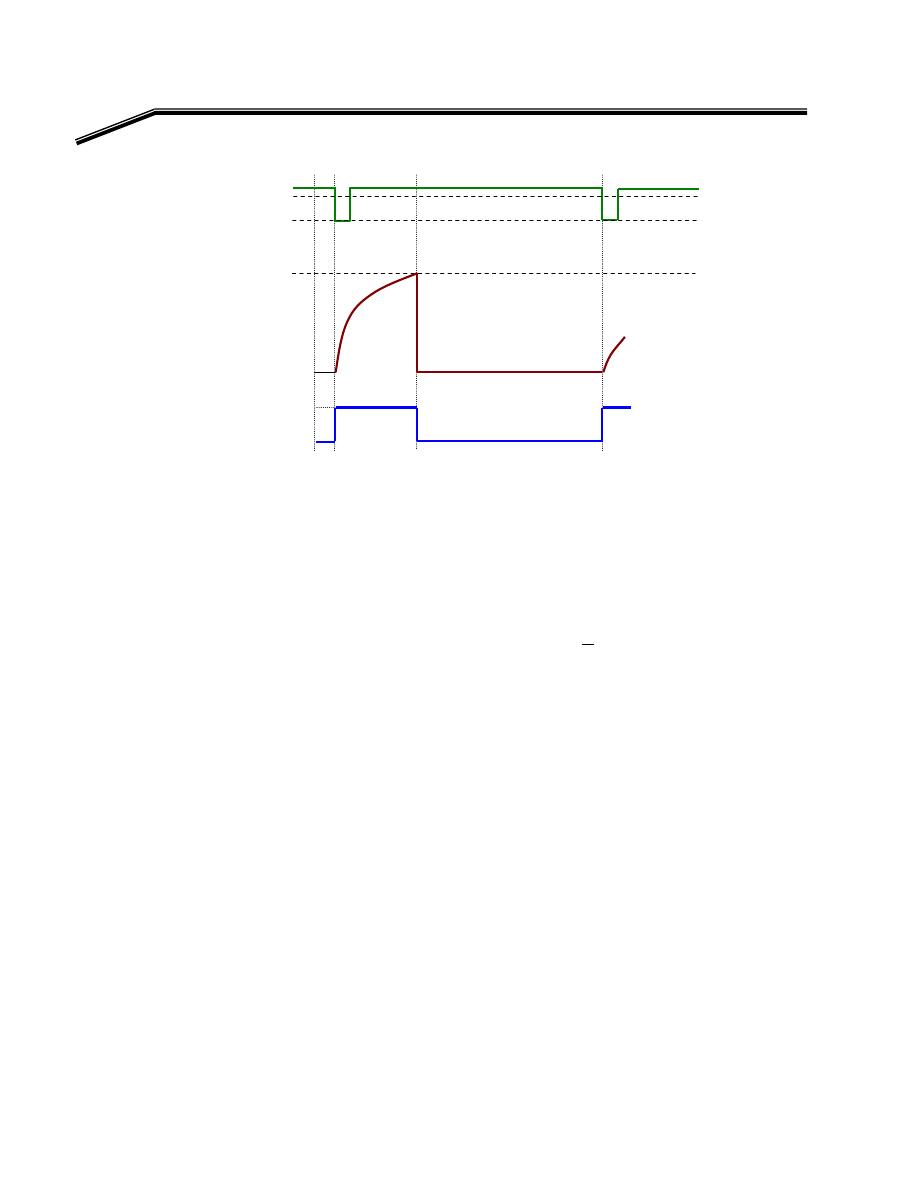

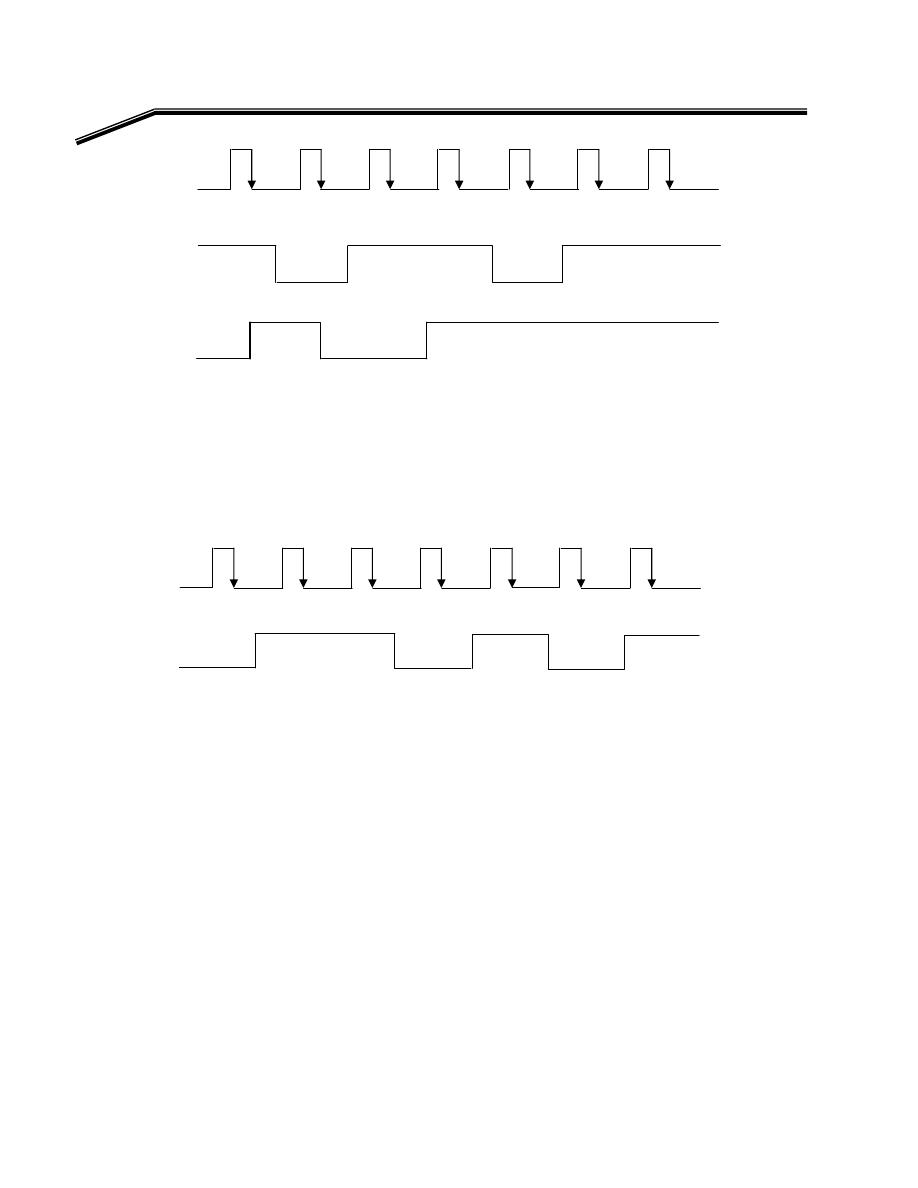

אאא

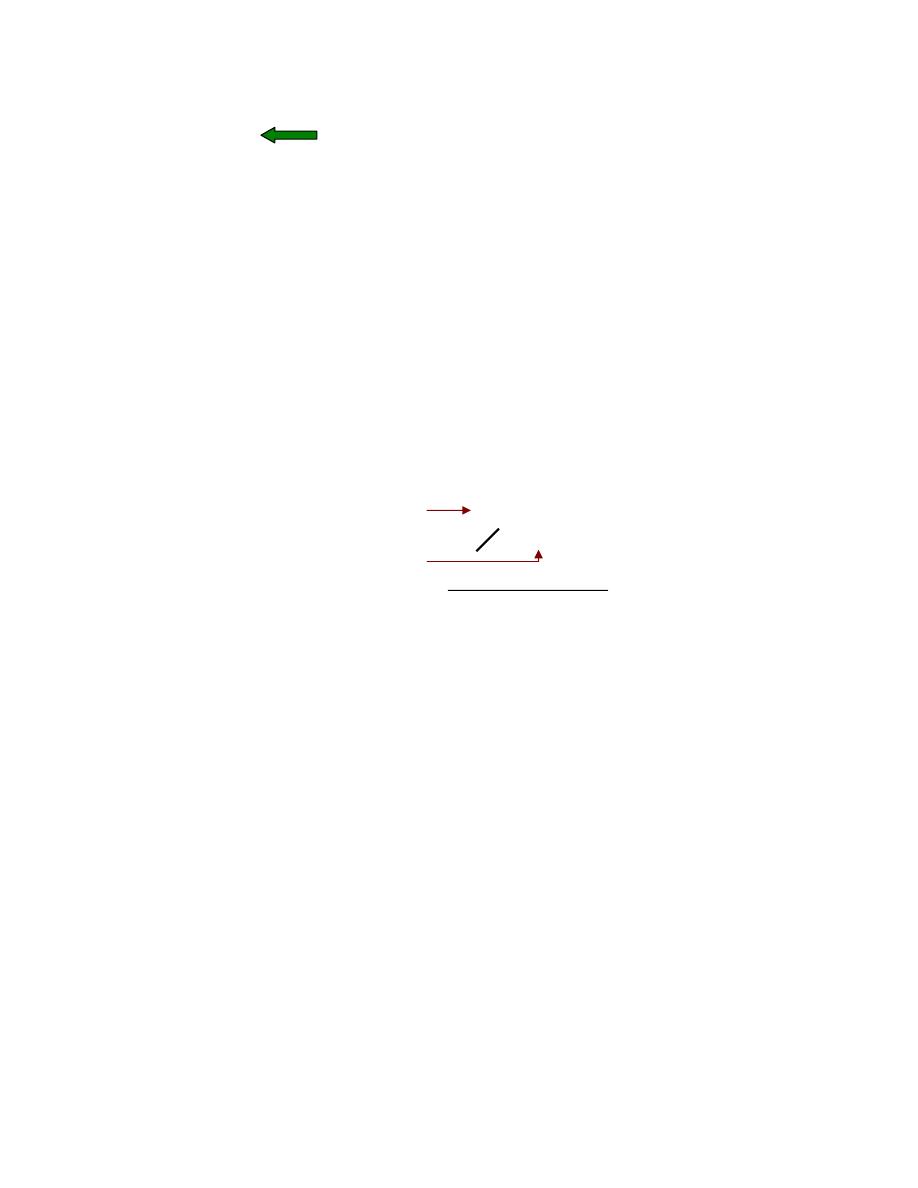

(Pulses)

א

א

(HIGH)

א

(LOW)

K

א

א

AND

אא،אא

א

K

،

F

٢

J

٣

E

א

A

,

B

(

)١

א

א

t

١

אא

Y

א

(

)١

،

אא

t

٢

א،

A

אא

٧٤١

א

א

אאאא

א

-

٠٤

-

(

)٠

א

B

א

Y

(

)٠

،

אאא

אא

K

אאא

אאא

(Timing Diagram)

K

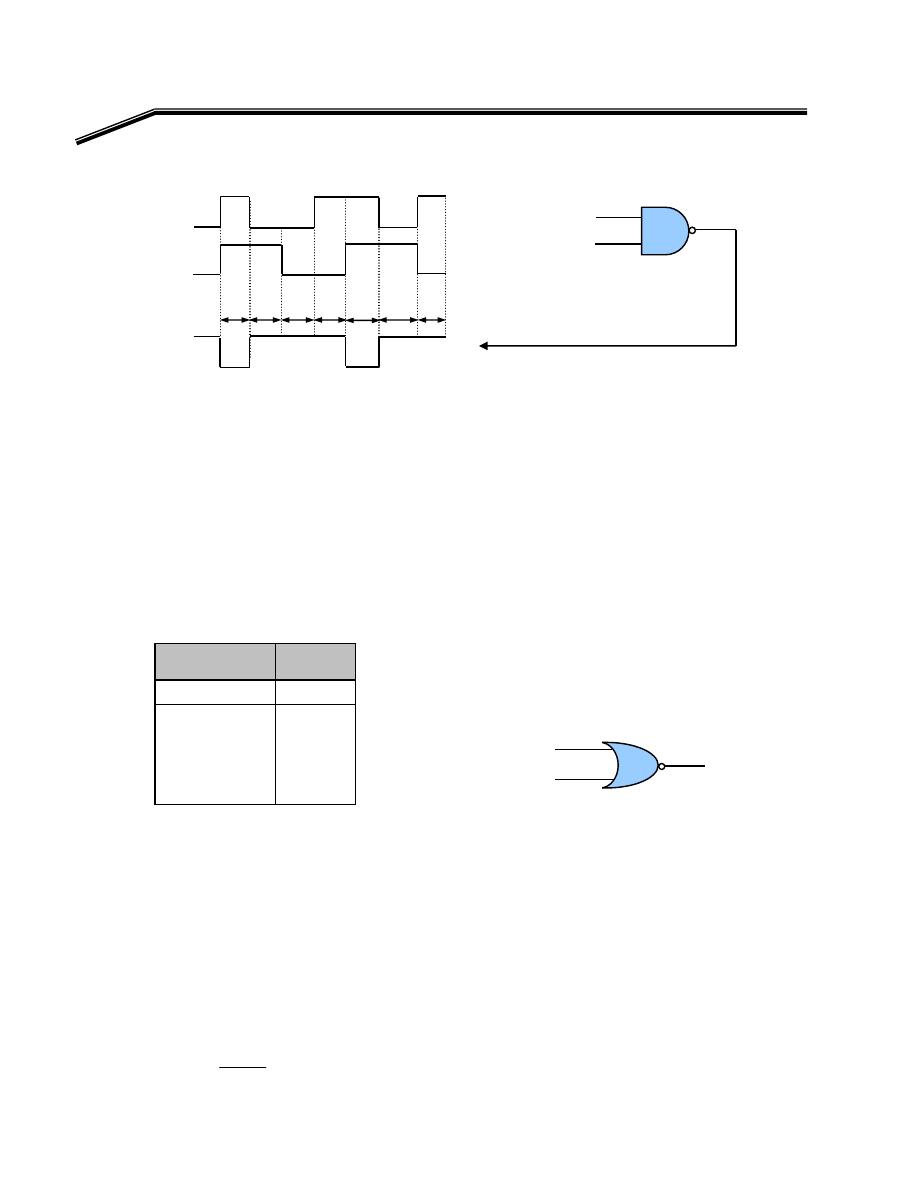

F

٢

J

٣

E

אאא

AND

K

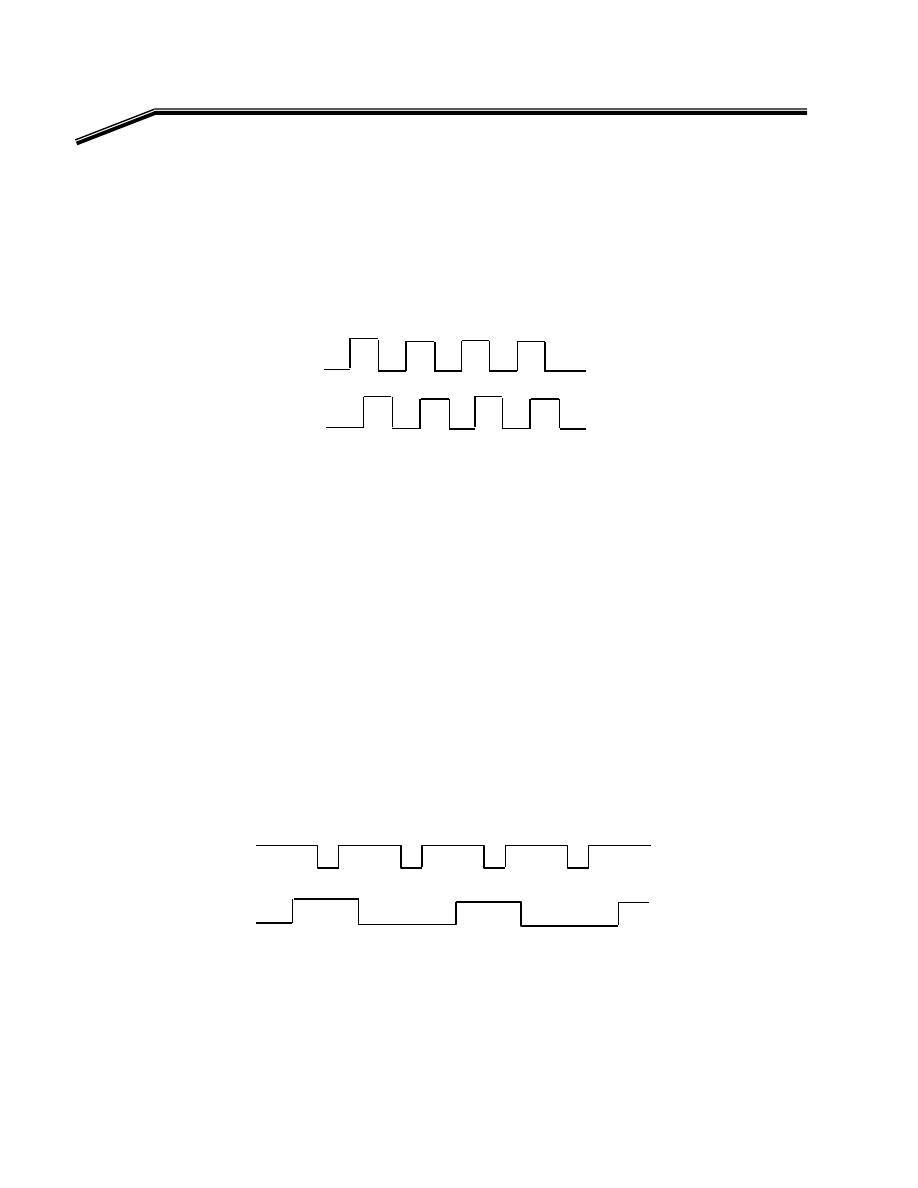

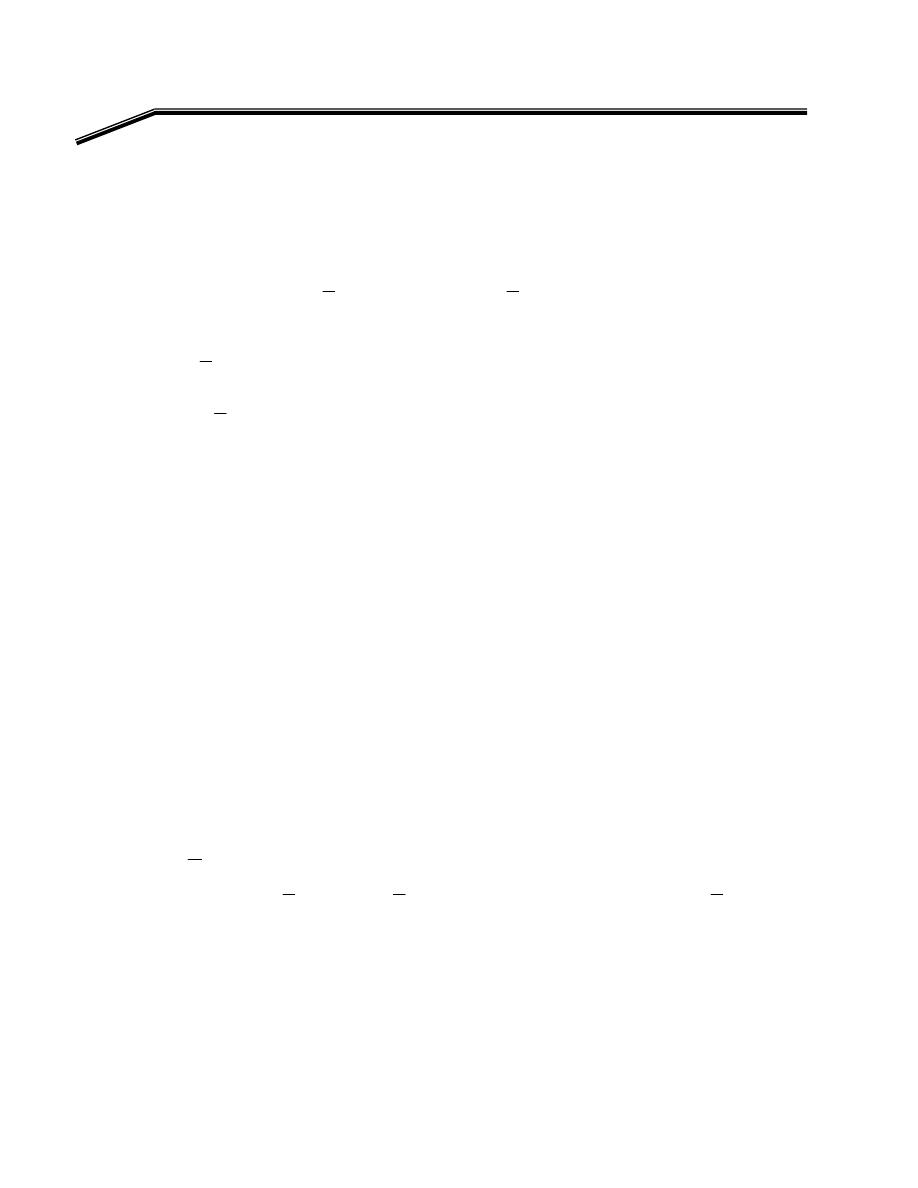

٢

J

٤

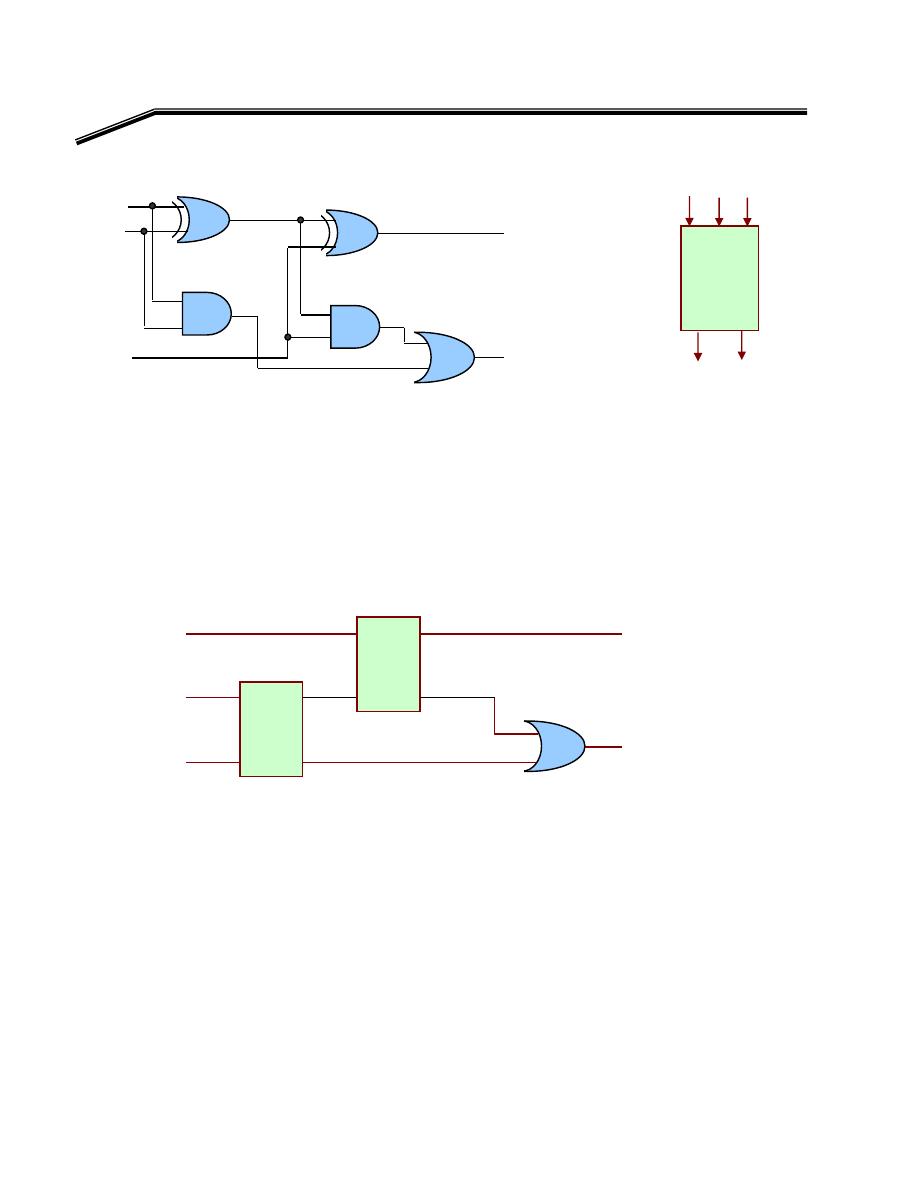

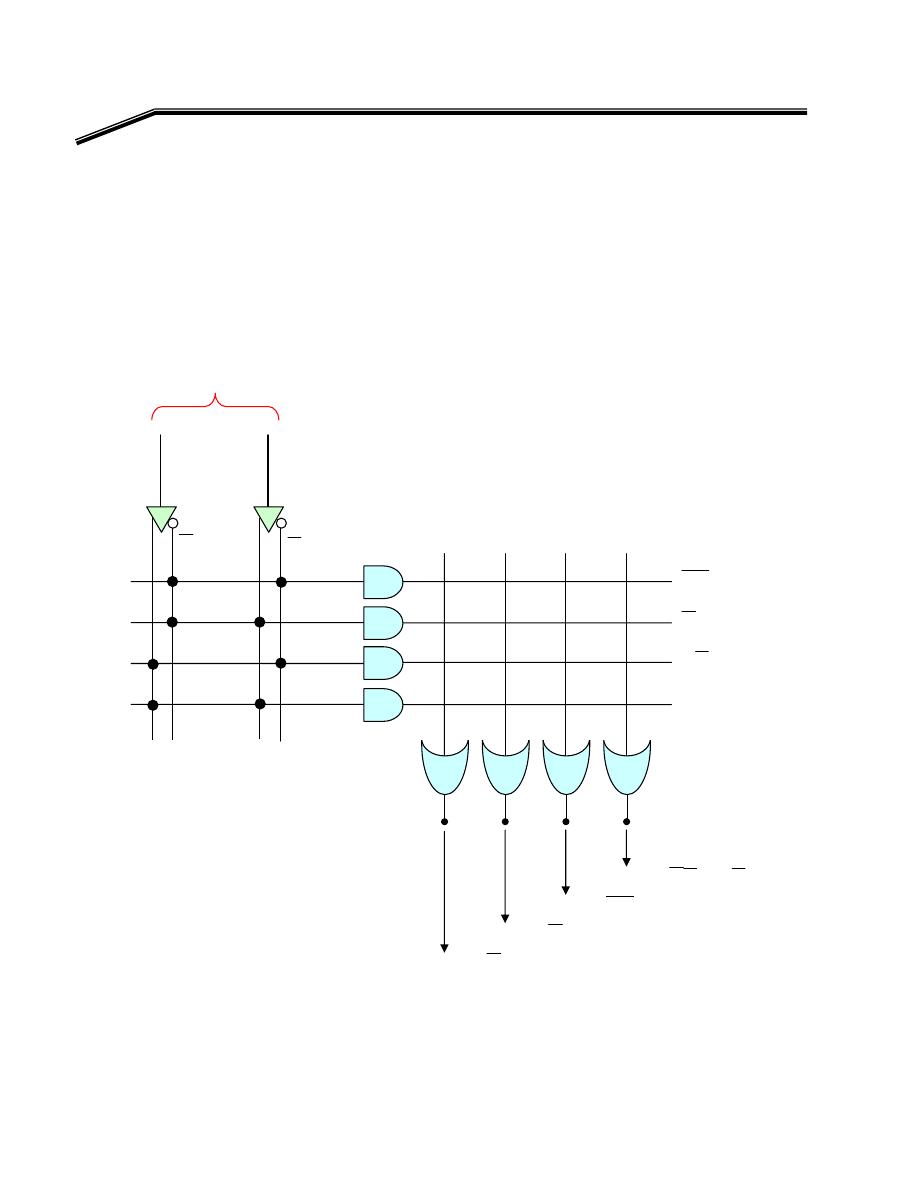

א

OR

OR Gate

אא

OR

אאאאאאאא

K

אא

OR

،א

אאא

(Logical Addition)

אאאאאאא،

F

٢

J

٤

E

K

אא

AND

א

A

,

B

(

)٠

א

(Open)

(

)١

א

(Closed)

K

F

٢

J

٤

E

אא

OR

אא

K

F

٢

J

٤

E

אא،אאא

אא

(L)

א

K

Voltage Source

(B)

(A)

Y

B

A

t

٧

t

٦

t

٥

t

٤

t

٣

t

٢

t

١

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

١٤

-

L

B

A

F

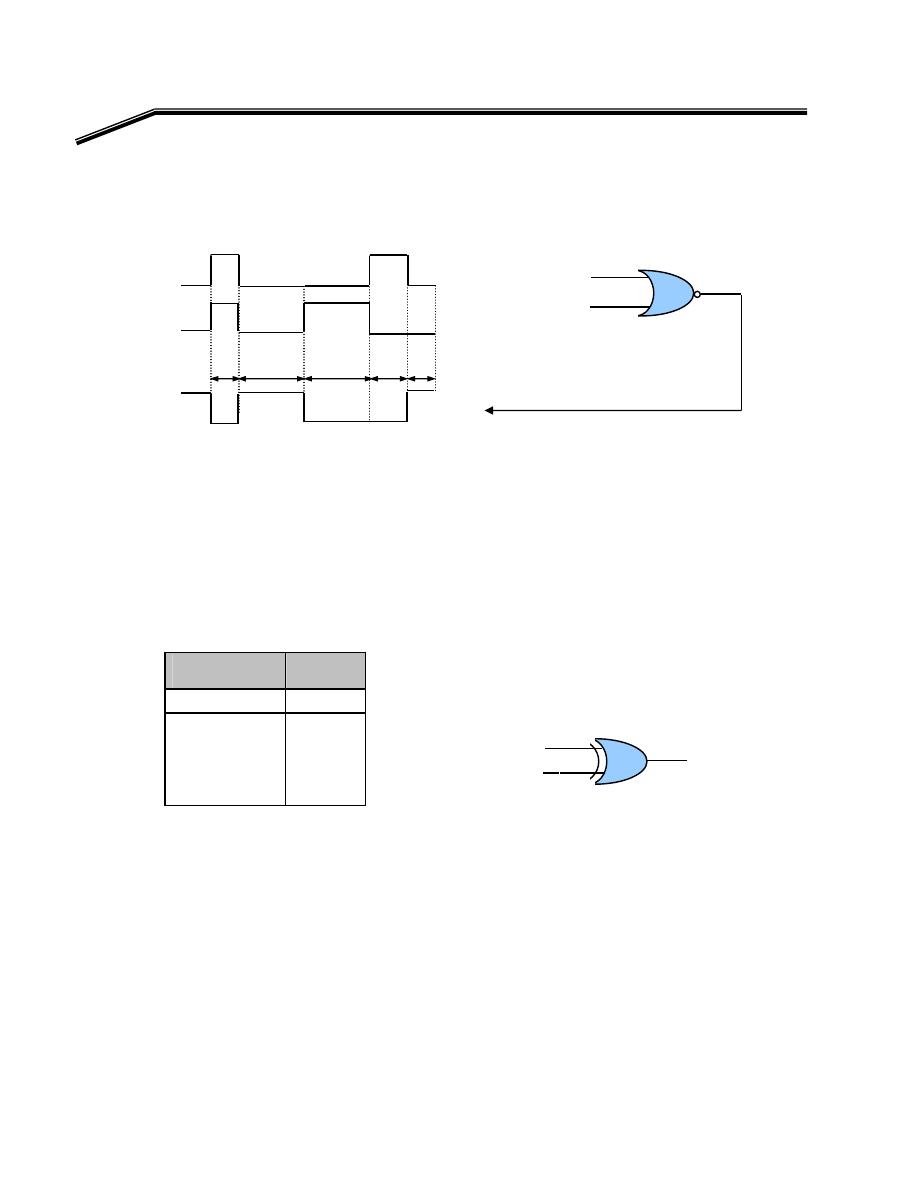

٢

J

٤

E

אא

F

٢

J

٤

KE

א

F

٢

J

٥

E

אאאא

OR

א،

A

,

B

א

Y

K

א

F

٢

J

٥

E

אא

OR

K

א

א

Y

B

A

٠

٠

٠

١

١

٠

١

٠

١

١

١

١

F

٢

J

٥

E

אא

OR

K

F

٢

J

٥

E

אא

OR

K

א

F

٢

J

٥

E

א

(

)١

א

א

(

)١

،

א

(

)٠

א

(

)٠

א

K

אאא

OR

א

W

Y = A + B

א

W

א

Y

A OR B

+)

OR

(

K

א

א

OR

،אא

א

AND

אאא

א

K

F

٢

J

٦

E

א

A

,

B

(

)١

אא

t

١

א

א

Y

א

(

)١

،

אא

t

٢

א،

A

(

)٠

א

B

א

Y

(

)١

،

אאאאא

K

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٢٤

-

F

٢

J

٦

E

אאא

OR

K

٢

J

٥

א

NOT

F

א

E

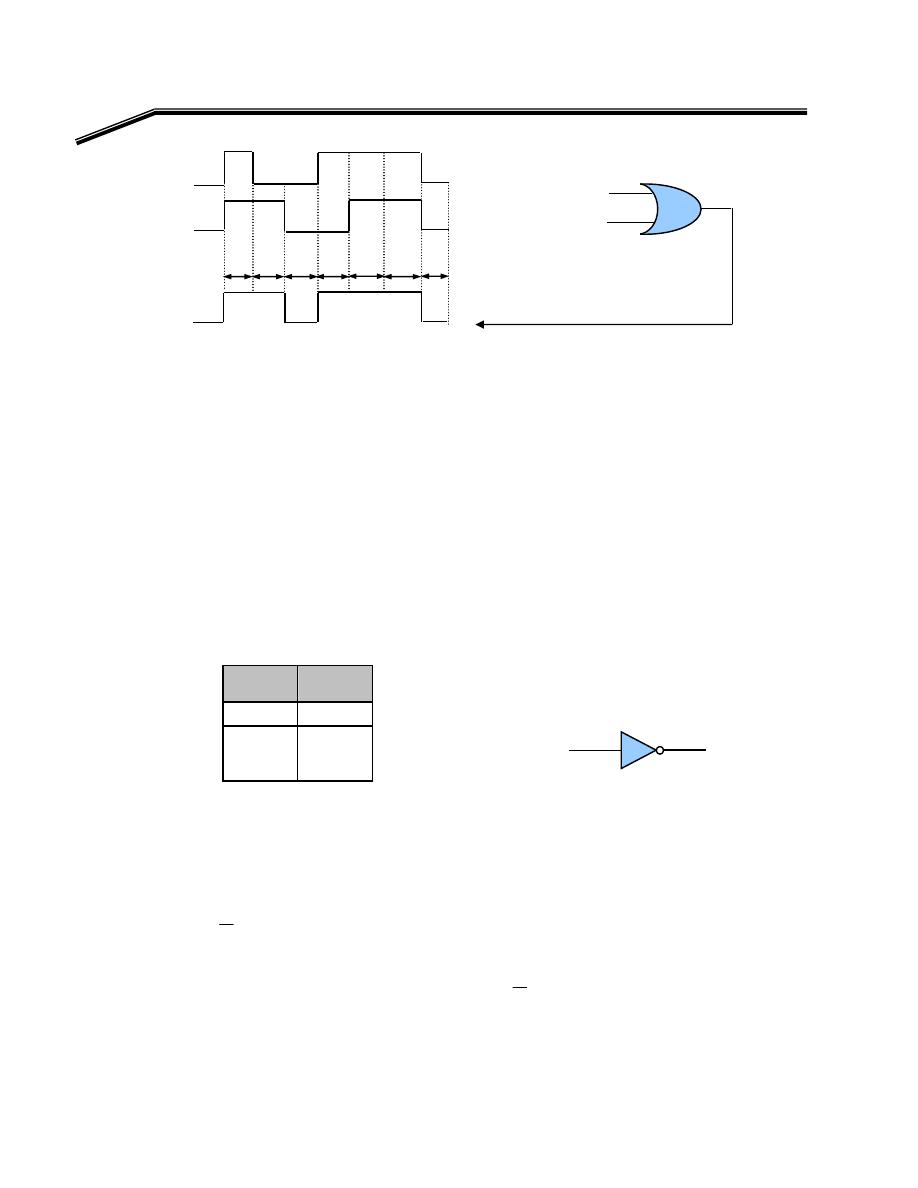

NOT Gate (INVERTER)

אא

NOT

א

(Inversion)

א

(Complementation)

K

א،אאא

(

)١

א

(

)٠

،

א

(

)٠

(

)١

K

אא

NOT

אאא

K

F

٢

J

٧

E

א،אאאאא

F

٢

J

٦

E

אאא

K

א

א

Y

A

١

٠

٠

١

F

٢

J

٧

E

אא

NOT

K

F

٢

J

٦

E

אא

NOT

א

K

א،אאא

אא

W

Y =

A

אא

W

א

Y

not A

א

A

bar

א

،א

א

Y

A bar

F

A

E

K

٢

J

٦

א

NAND

NAND Gate

Y

A

B

Y

t

٧

t

٦

t

٥

t

٤

t

٣

t

٢

t

١

A

B

Y

A

אא

٧٤١

א

א

אאאא

א

-

٣٤

-

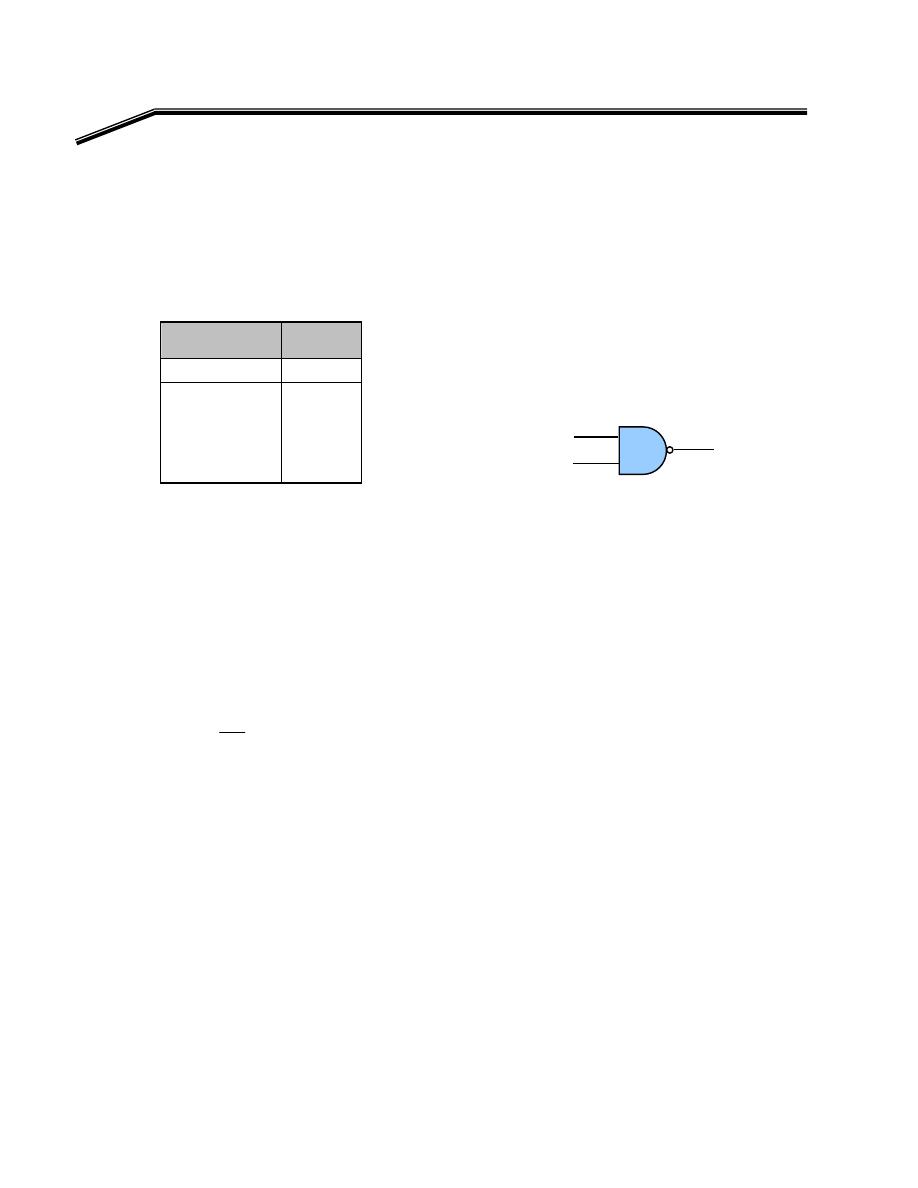

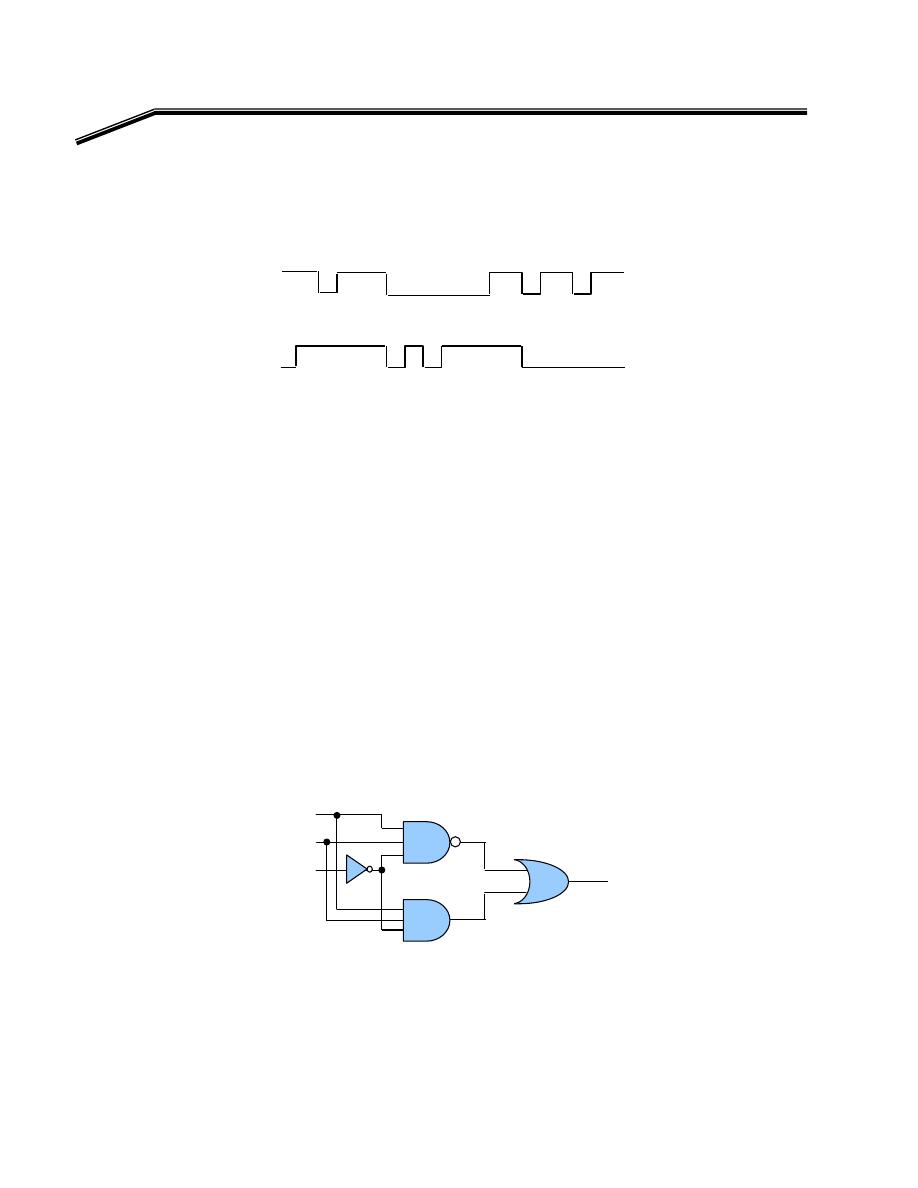

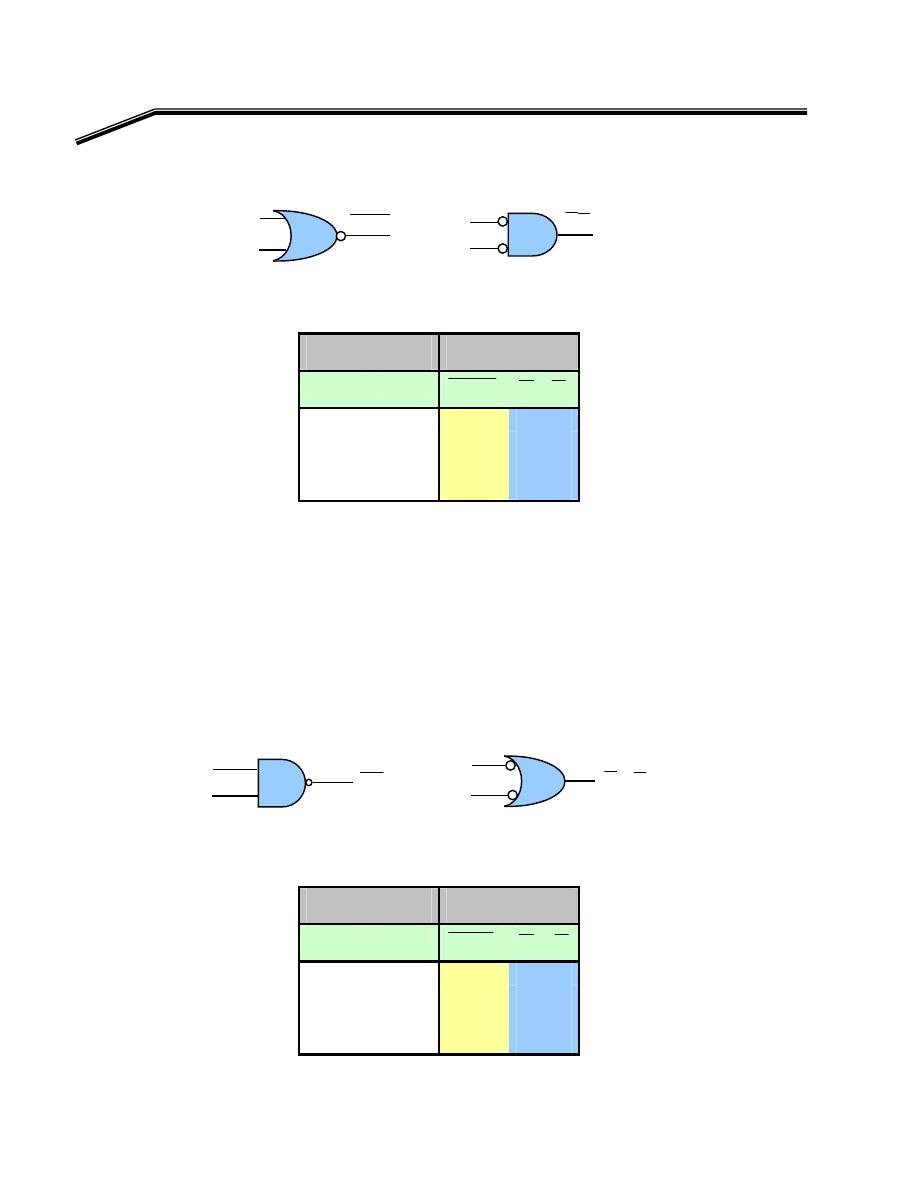

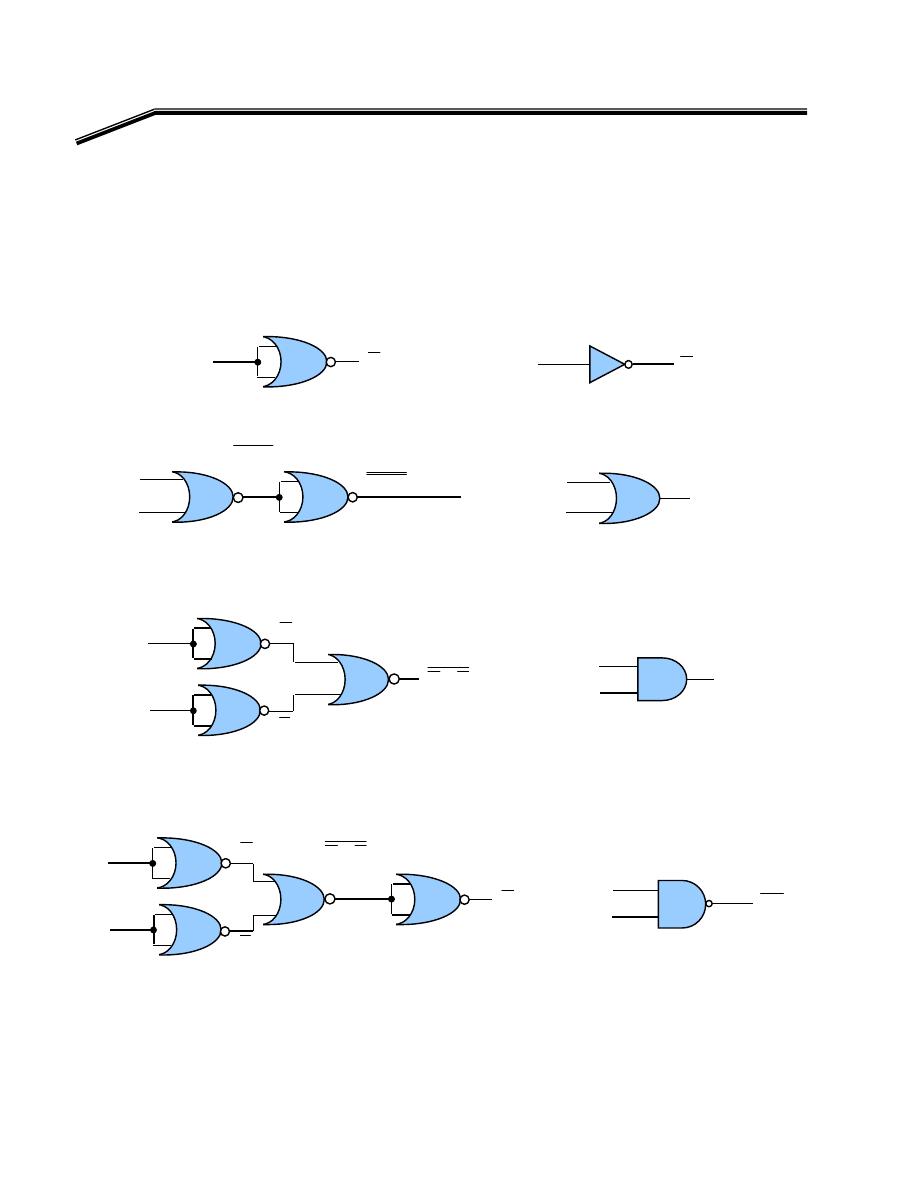

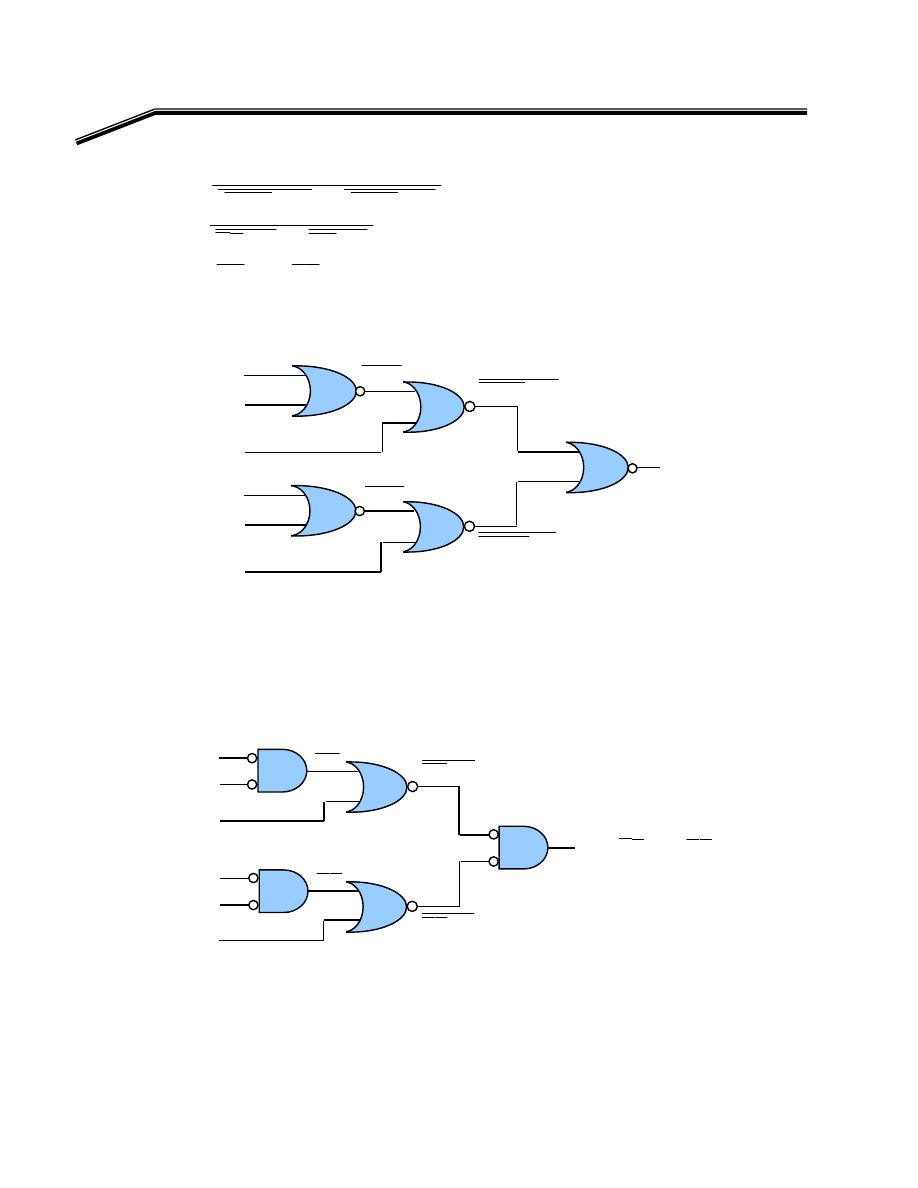

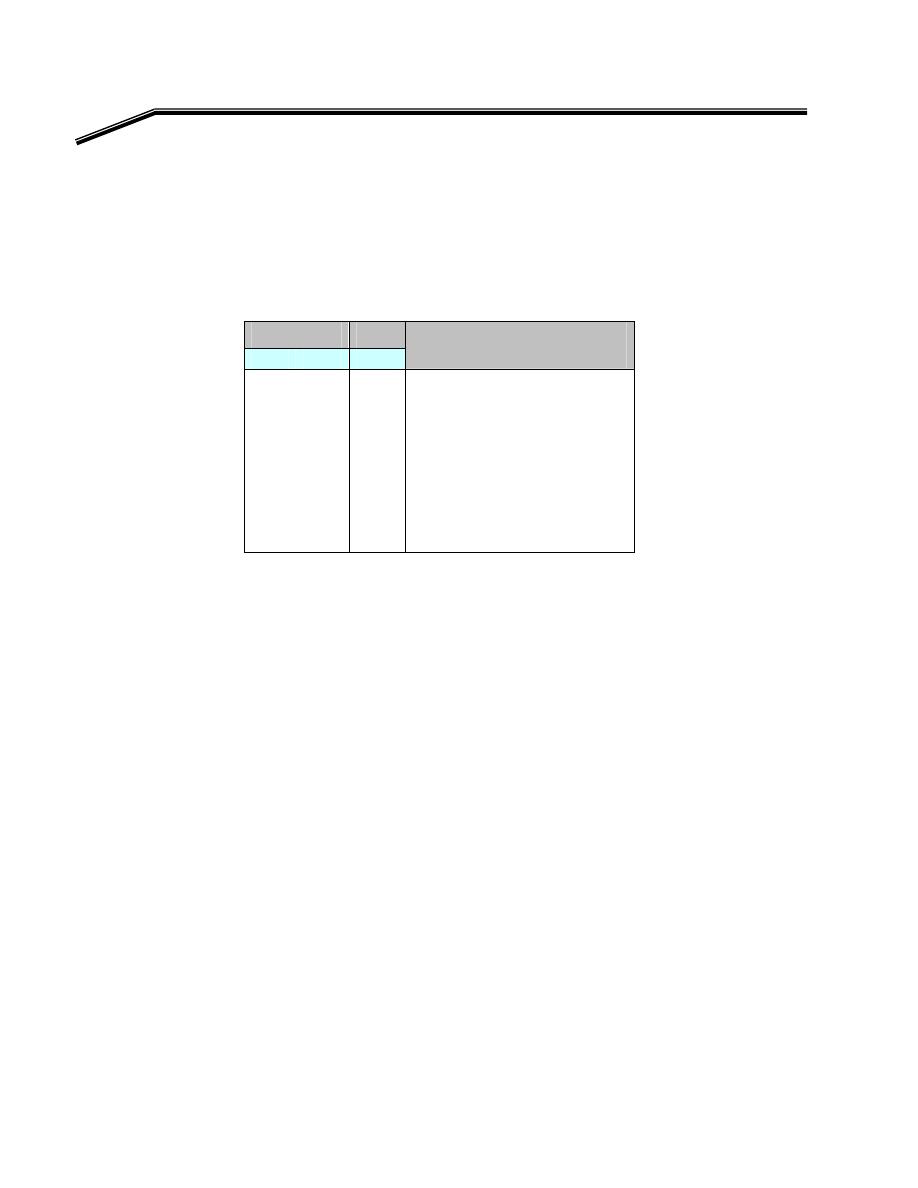

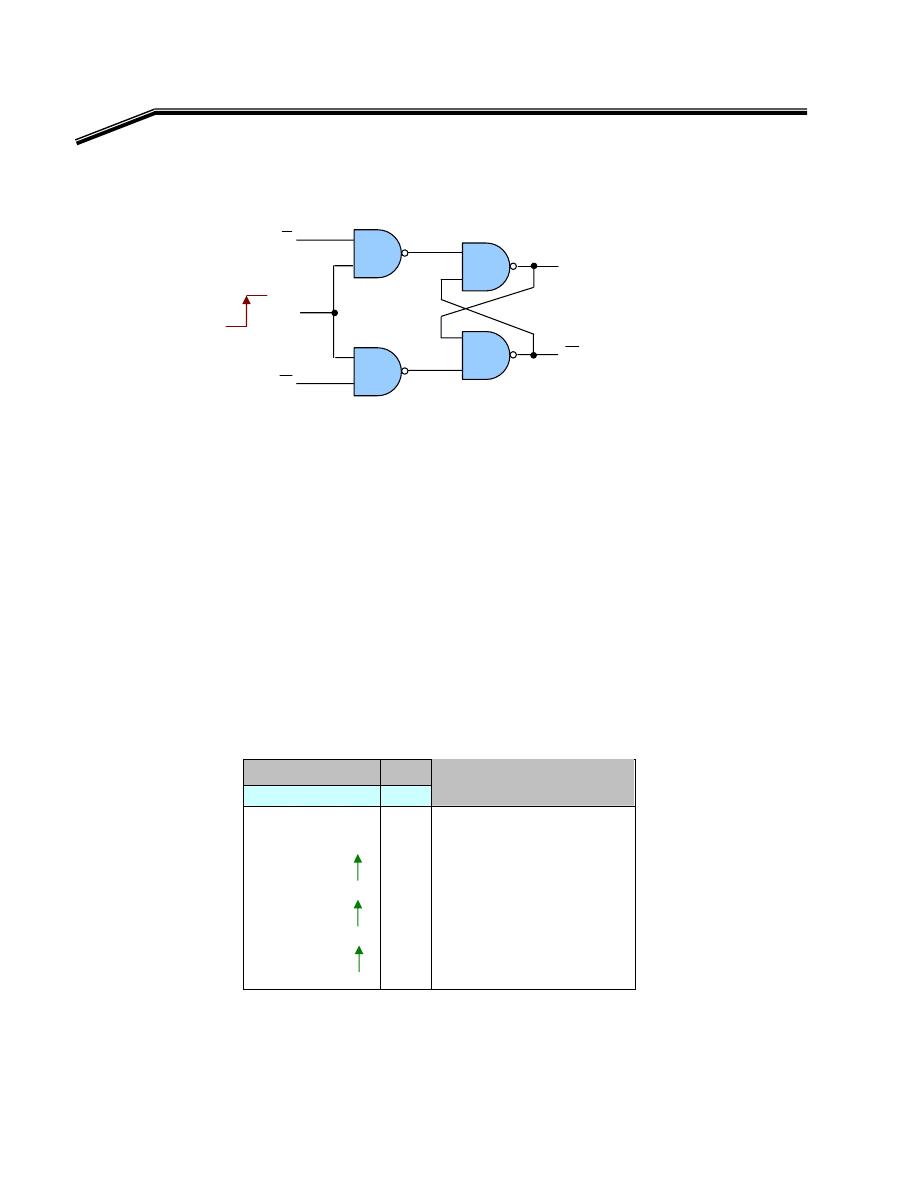

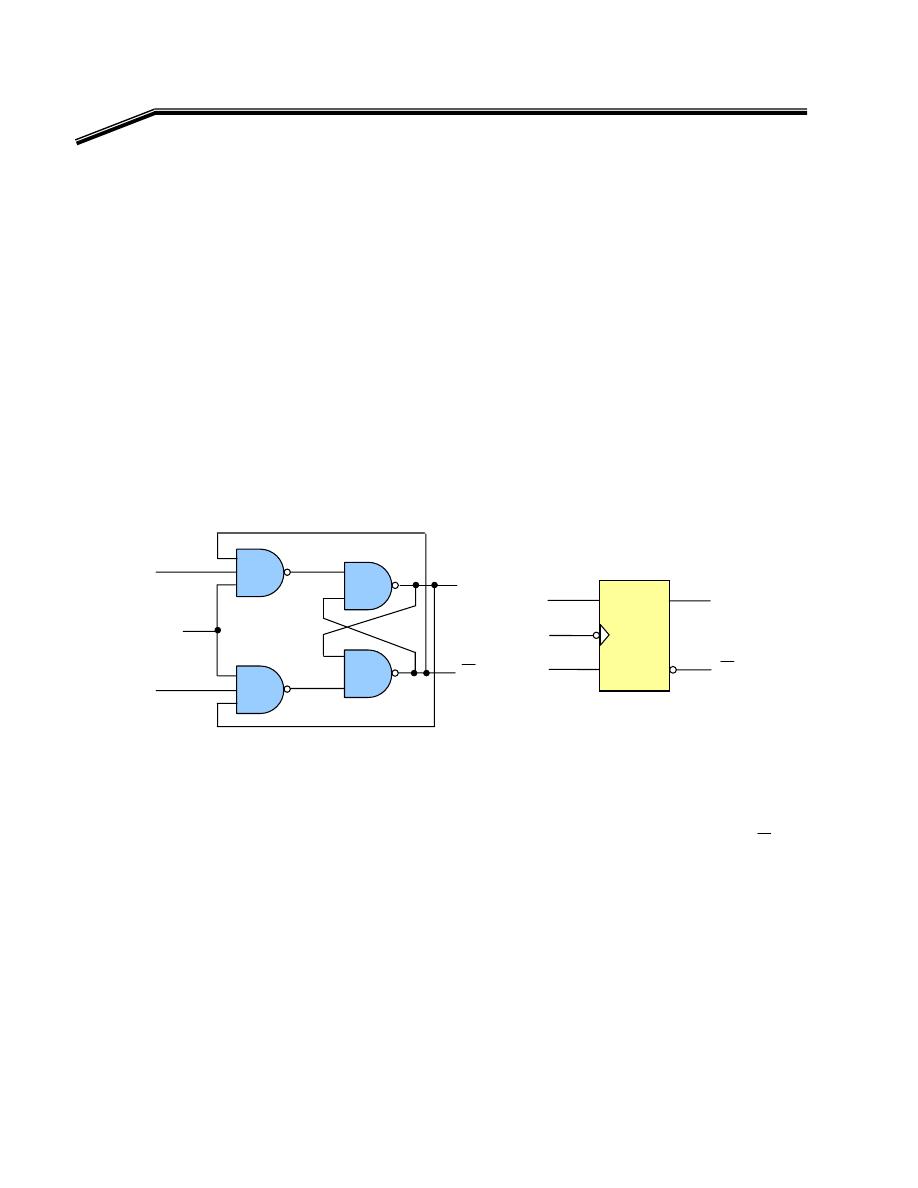

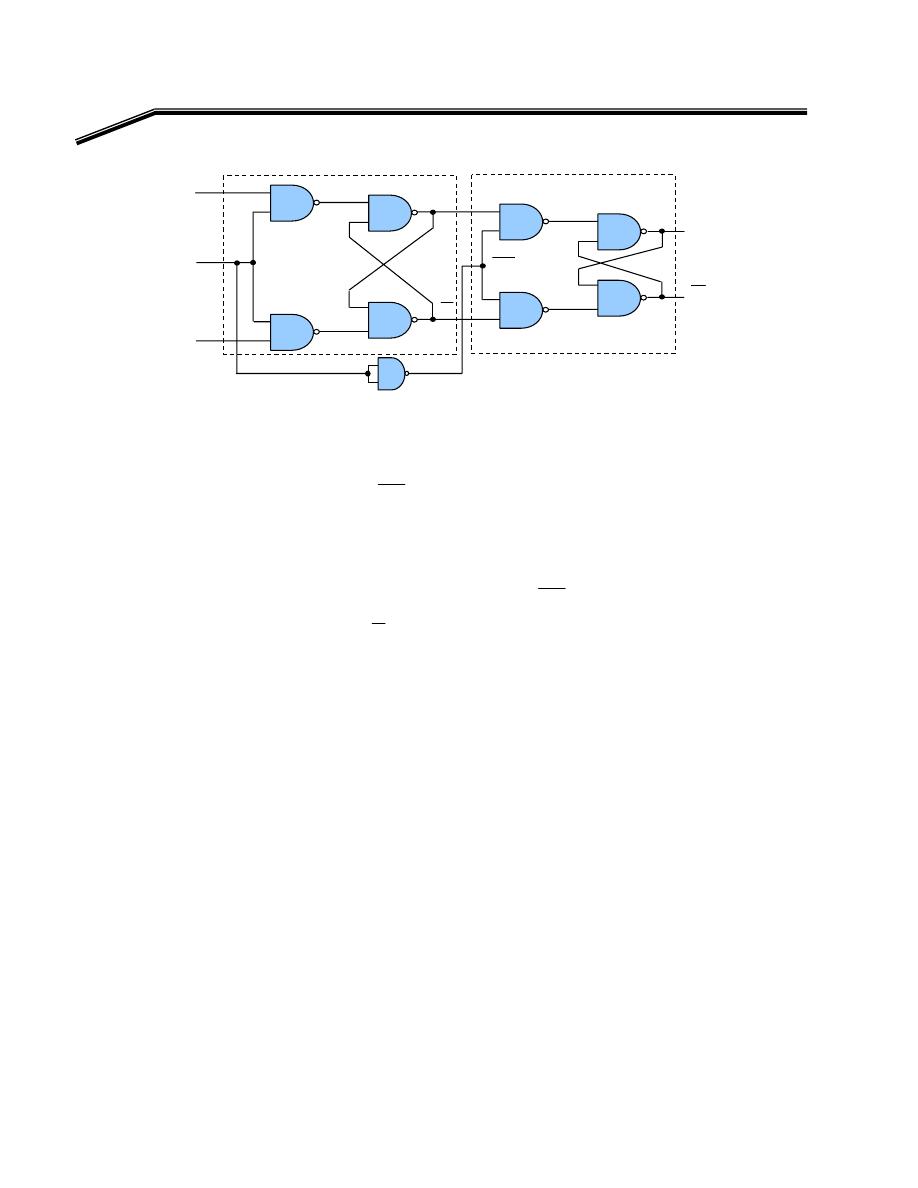

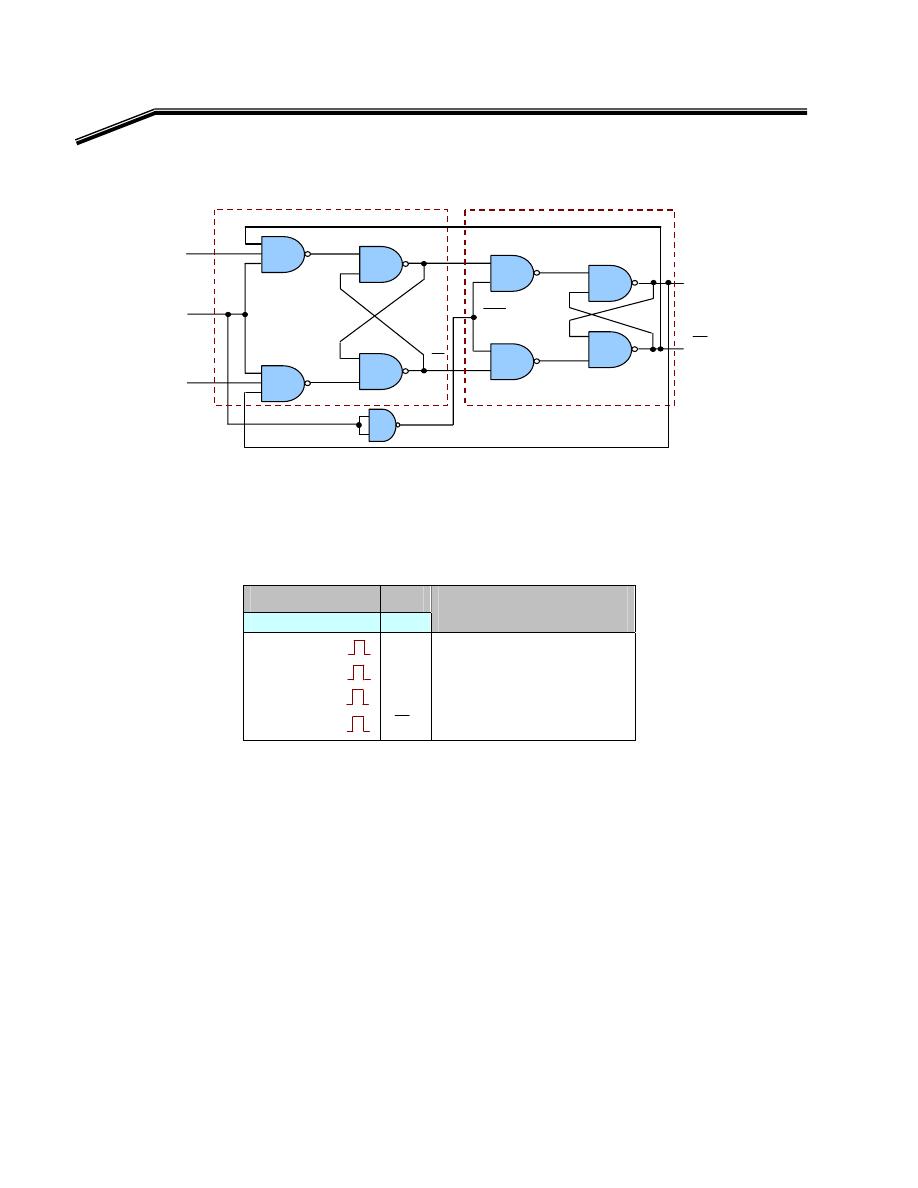

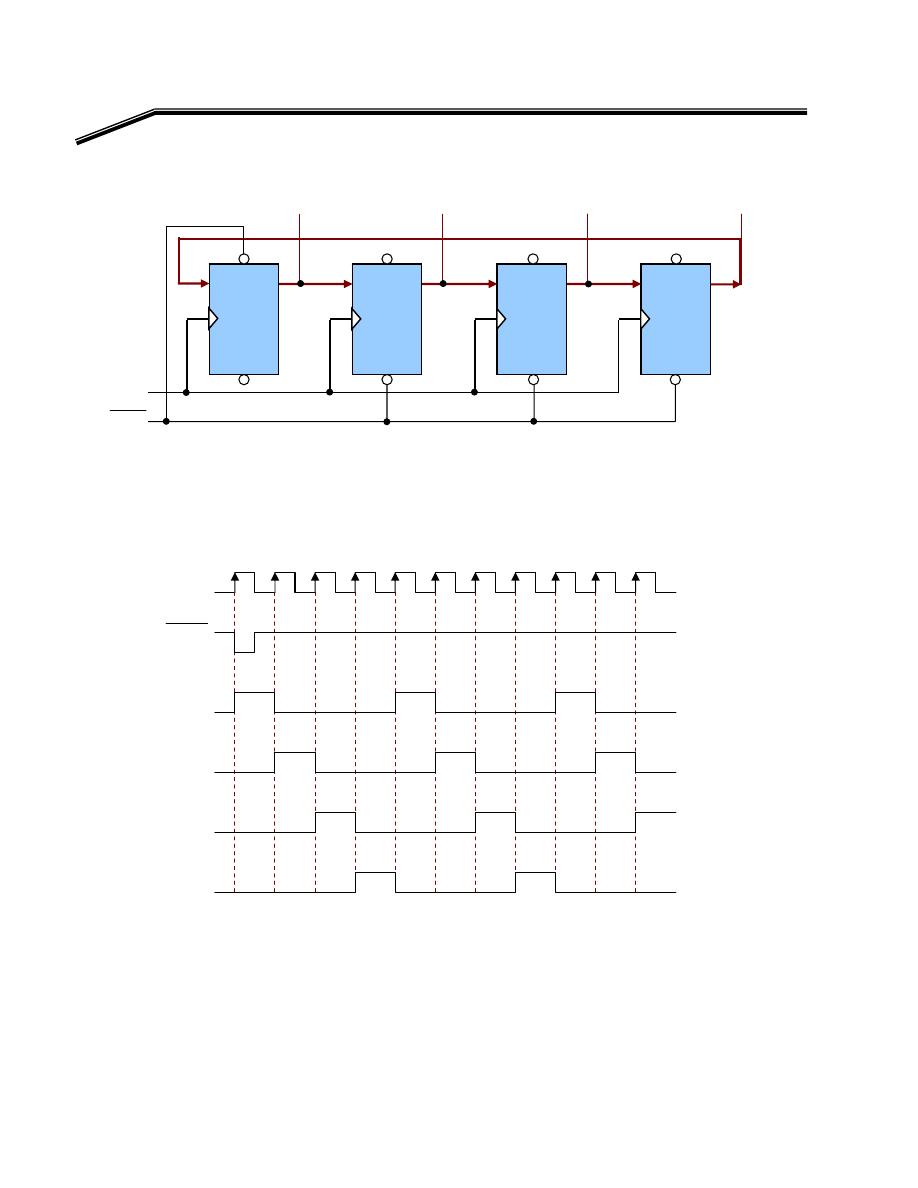

(NAND)

א

(NOT AND)

AND

אא،

אאאאא

AND

F

٢

J

٨

E

،

אאא

אא

א

AND

א

אאאא

K

F

٢

J

٧

E

אא

NAND

K

א

א

Y

B

A

١

٠

٠

١

١

٠

١

٠

١

٠

١

١

F

٢

J

٨

E

אא

NAND

K

F

٢

J

٧

E

אא

NAND

K

אא

(

)٠

אאא

(

)١

א،א

(

)١

אאא

(

)٠

،א

אאא

AND

K

אא

NAND

،אאאאאאא

אאאא

NOT,

OR, AND

،

אא،אא

NAND

א

W

Y =

AB

אא

NAND

،אא

אא

NAND

(

)٠

א

(

)١

K

F

٢

J

٩

E

א

A

,

B

(

)١

אא

t

١

א

א

Y

א

(

)٠

،

אא

t

٢

א،

A

(

)٠

א

B

(

)١

א

Y

(

)١

،

אאא

אא

K

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٤٤

-

Y

B

A

F

٢

J

٩

E

אאא

NAND

K

٢

J

٧

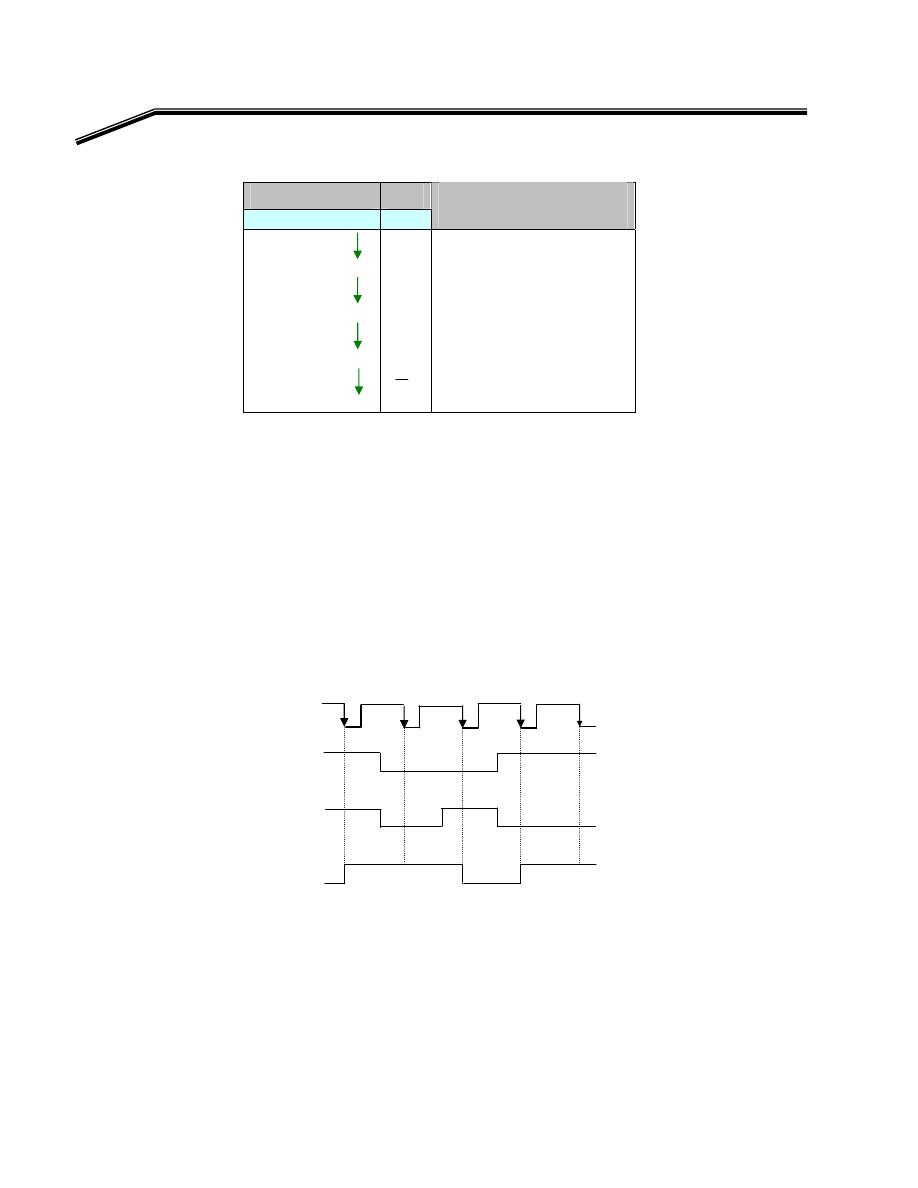

א

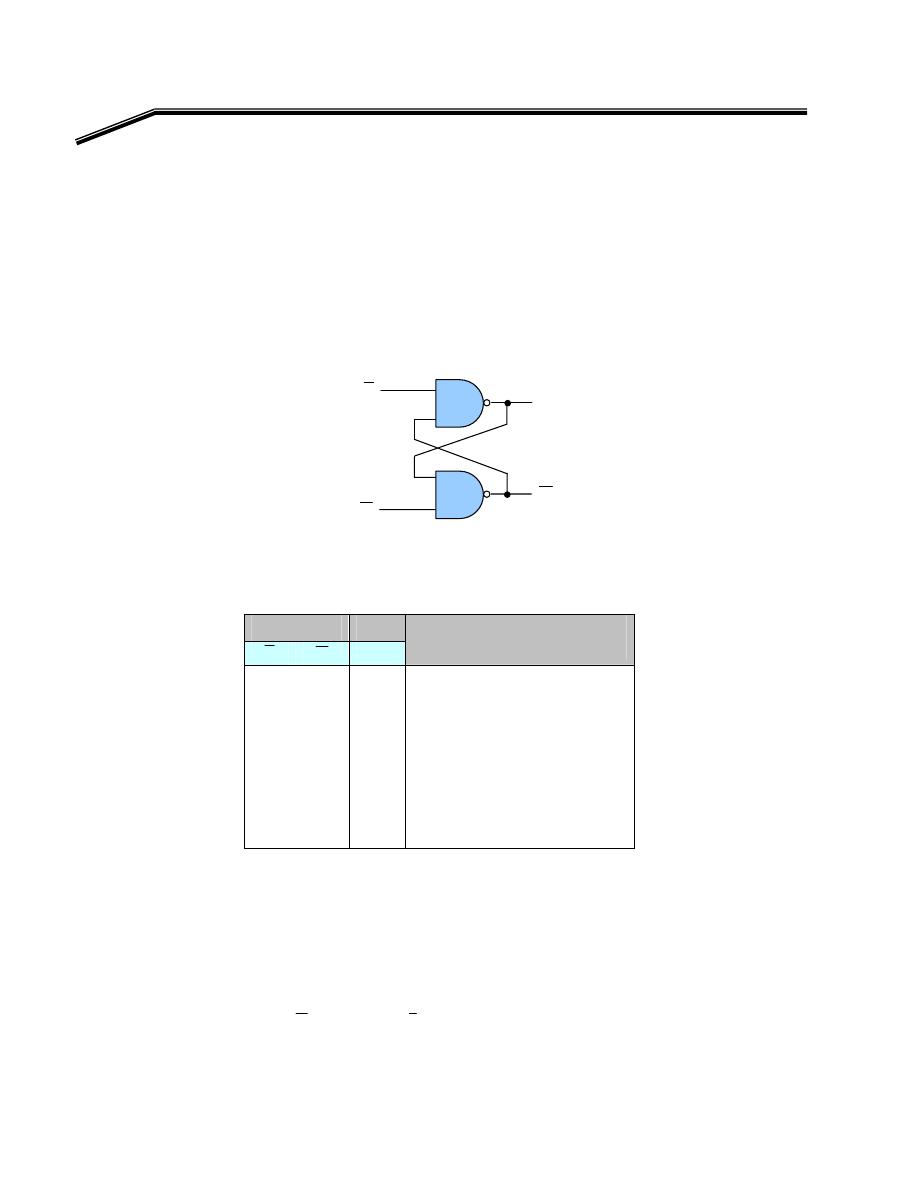

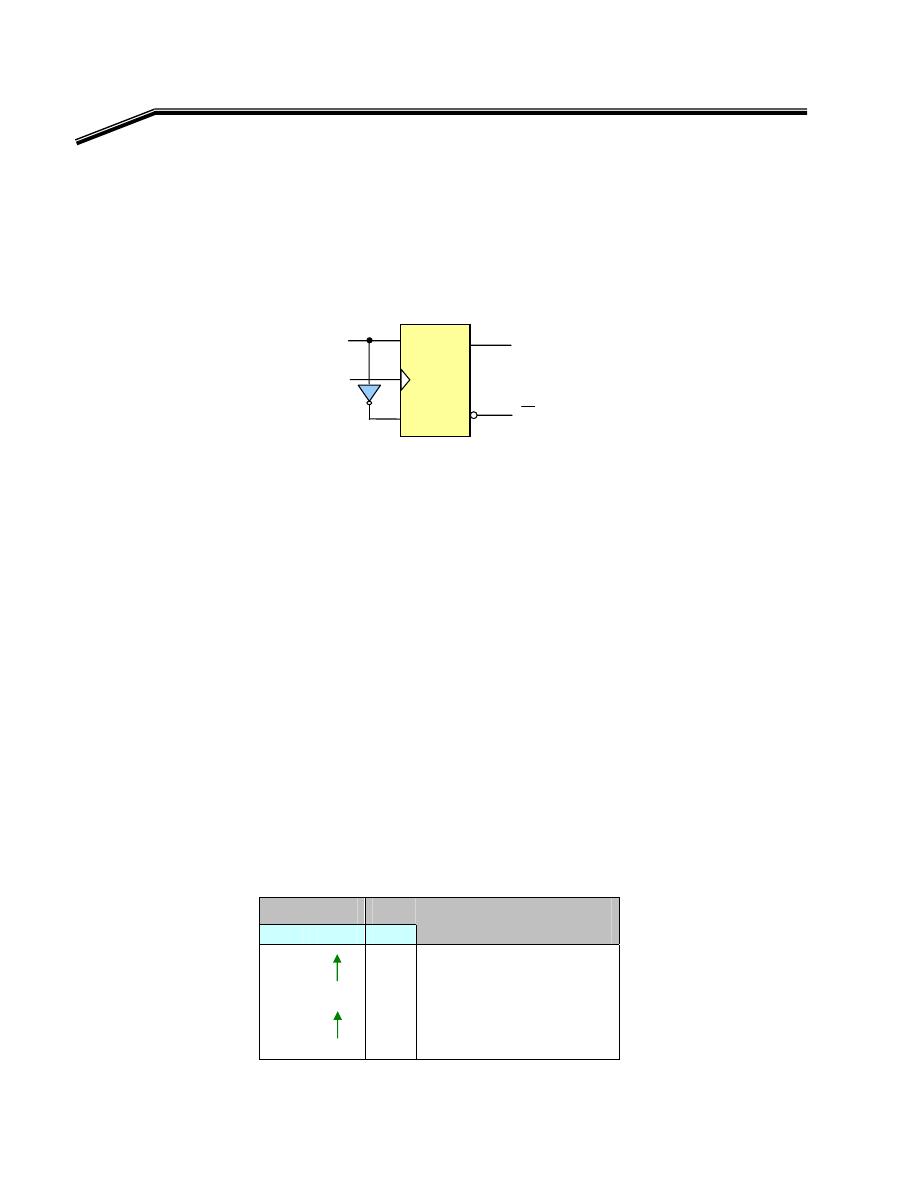

NOR

NOR Gate

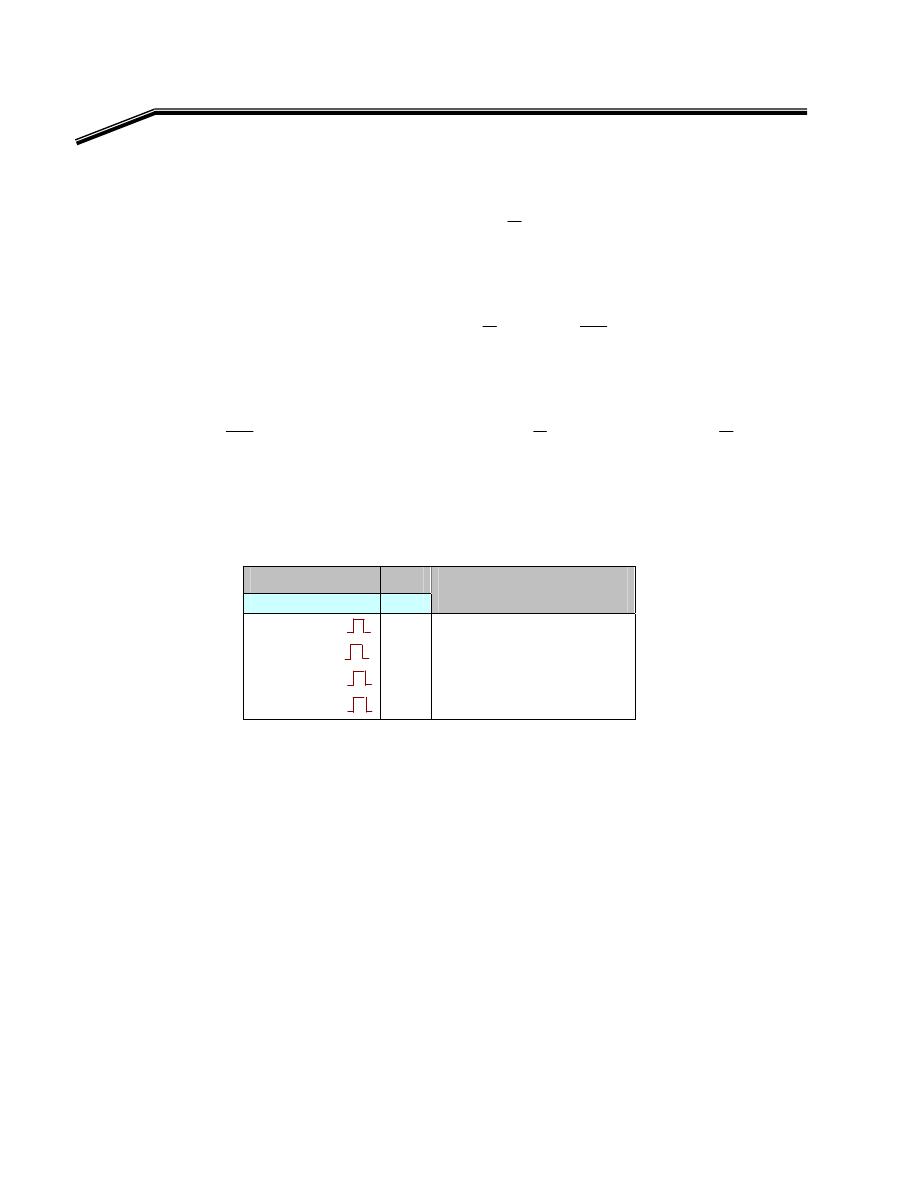

(NOR)

א

(NOT OR)

OR

אא،

אאא

(NOT gate)

אא

OR

F

٢

J

٠١

E

،

אאאא

NOR

K

אא

NOR

F

٢

J

٨

KE

א

א

Y

B

A

١

٠

٠

٠

١

٠

٠

٠

١

٠

١

١

F

٢

J

٠١

E

אא

NOR

K

F

٢

J

٨

E

אא

NOR

K

אא

(Y)

(

)٠

אא

א

(

)١

א

א،

(

)١

אא

(

)٠

א

K

אא

NOR

אאא

NAND

אאאאאא

א،א

NOT, OR, AND

،

K

א

אא

NOR

W

Y =

B

A

+

Y

t

٧

t

٦

t

٥

t

٤

t

٣

t

٢

t

١

A

B

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٥٤

-

Y

A

B

F

٢

J

١١

E

א

NOR

א

A

,

B

א

،א

אא

NOR

אא

(Y)

א

K

F

٢

J

١١

E

אאא

NOR

K

٢

J

٨

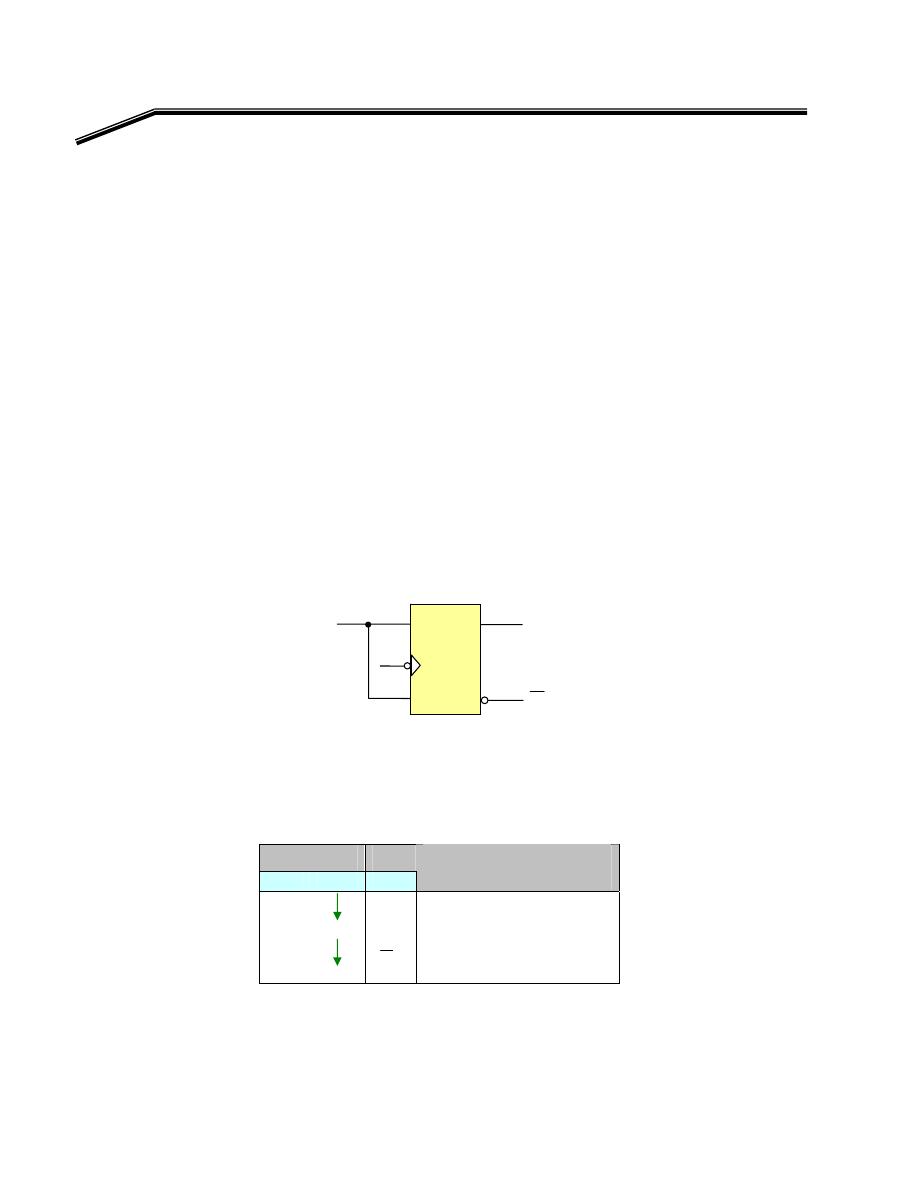

א

OR

א

F

א

E

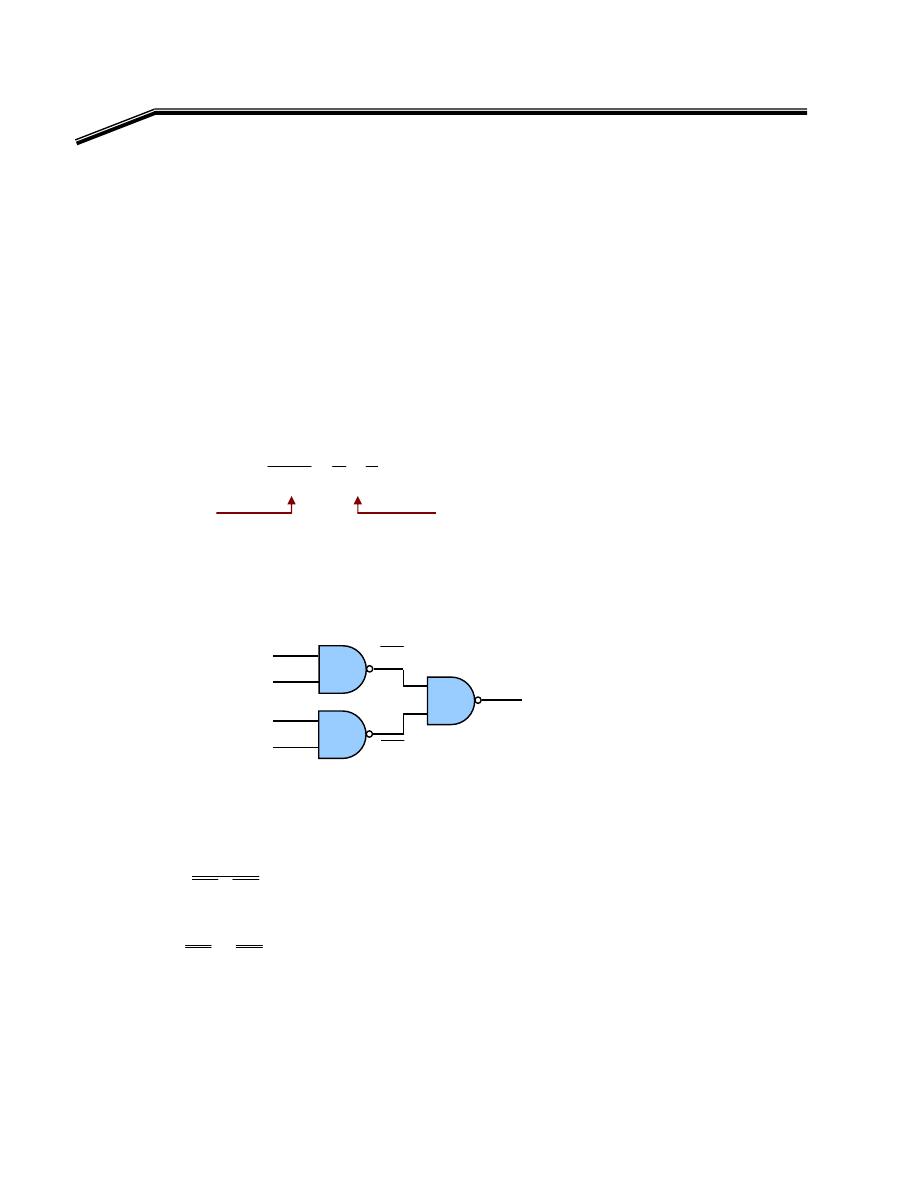

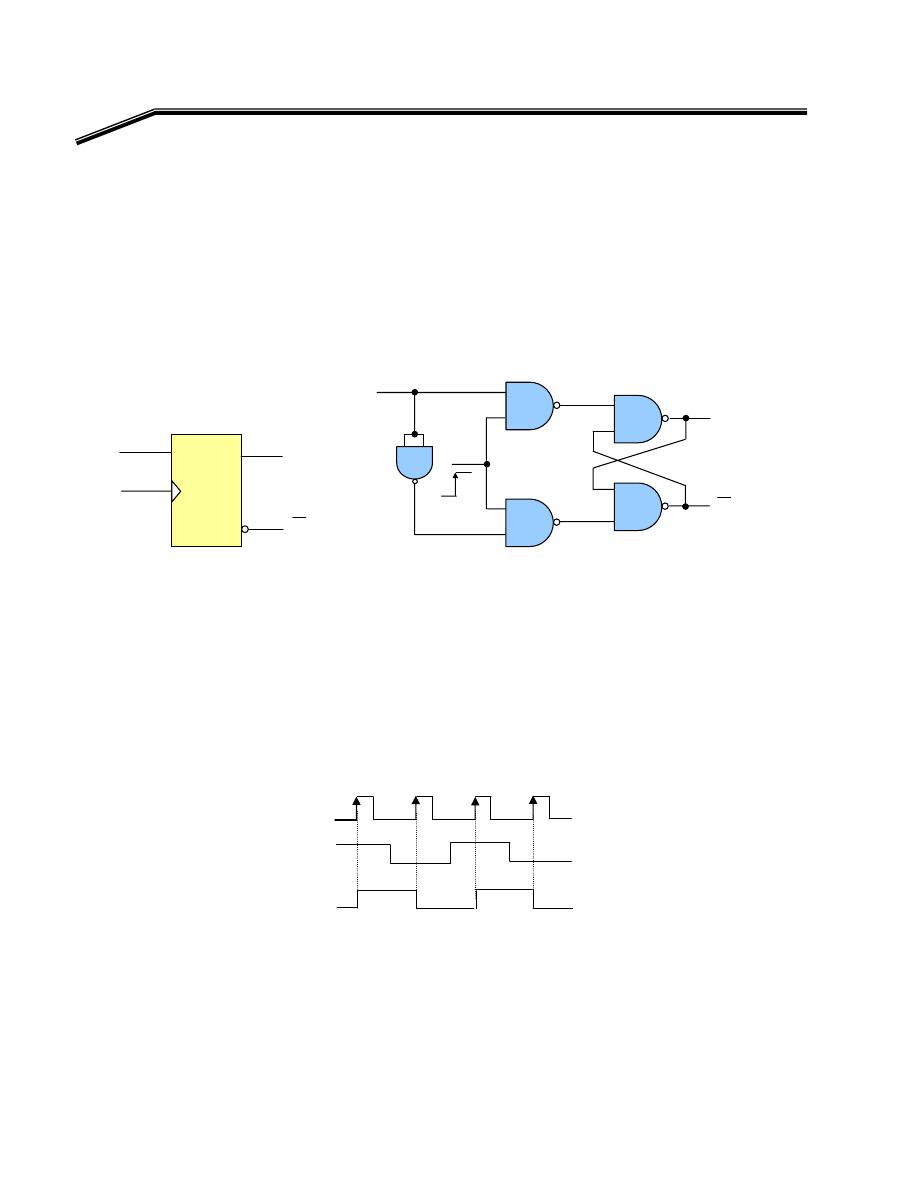

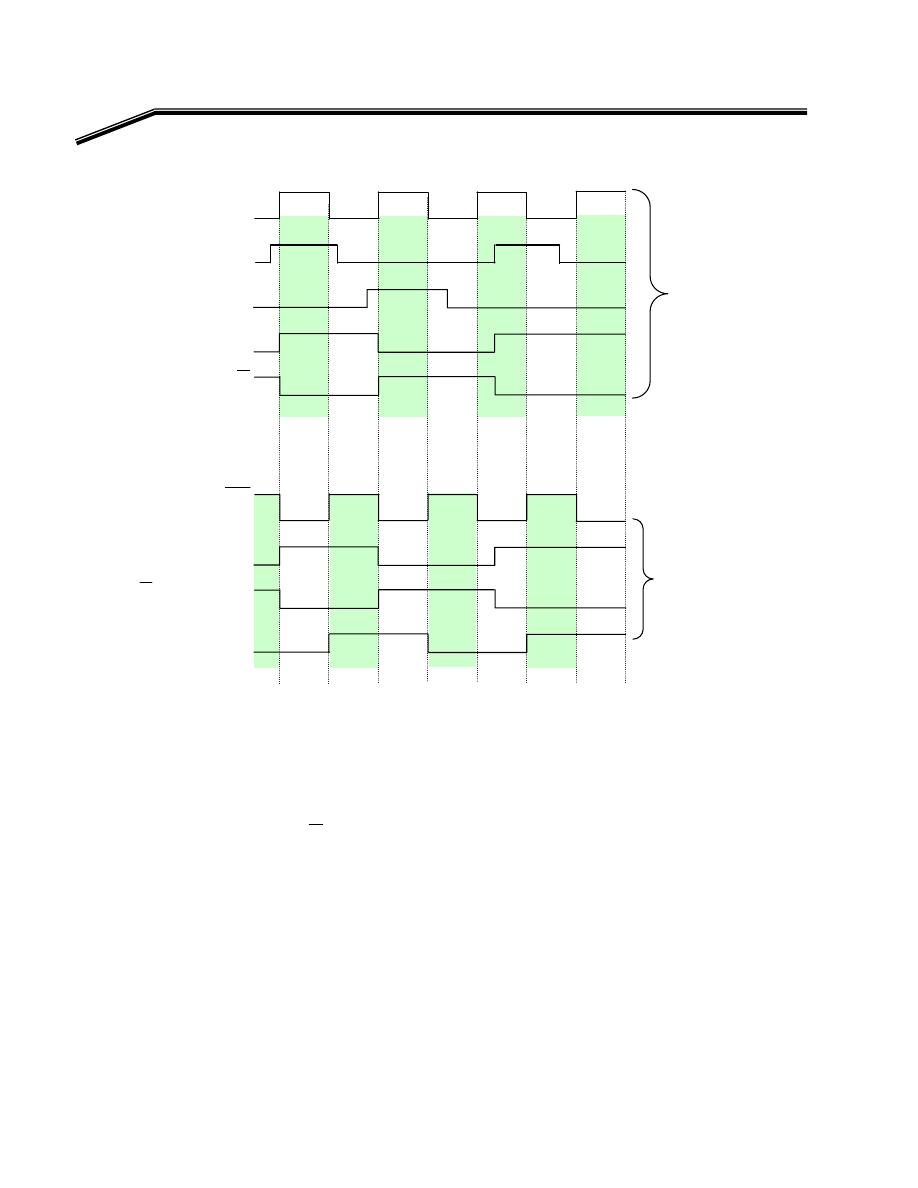

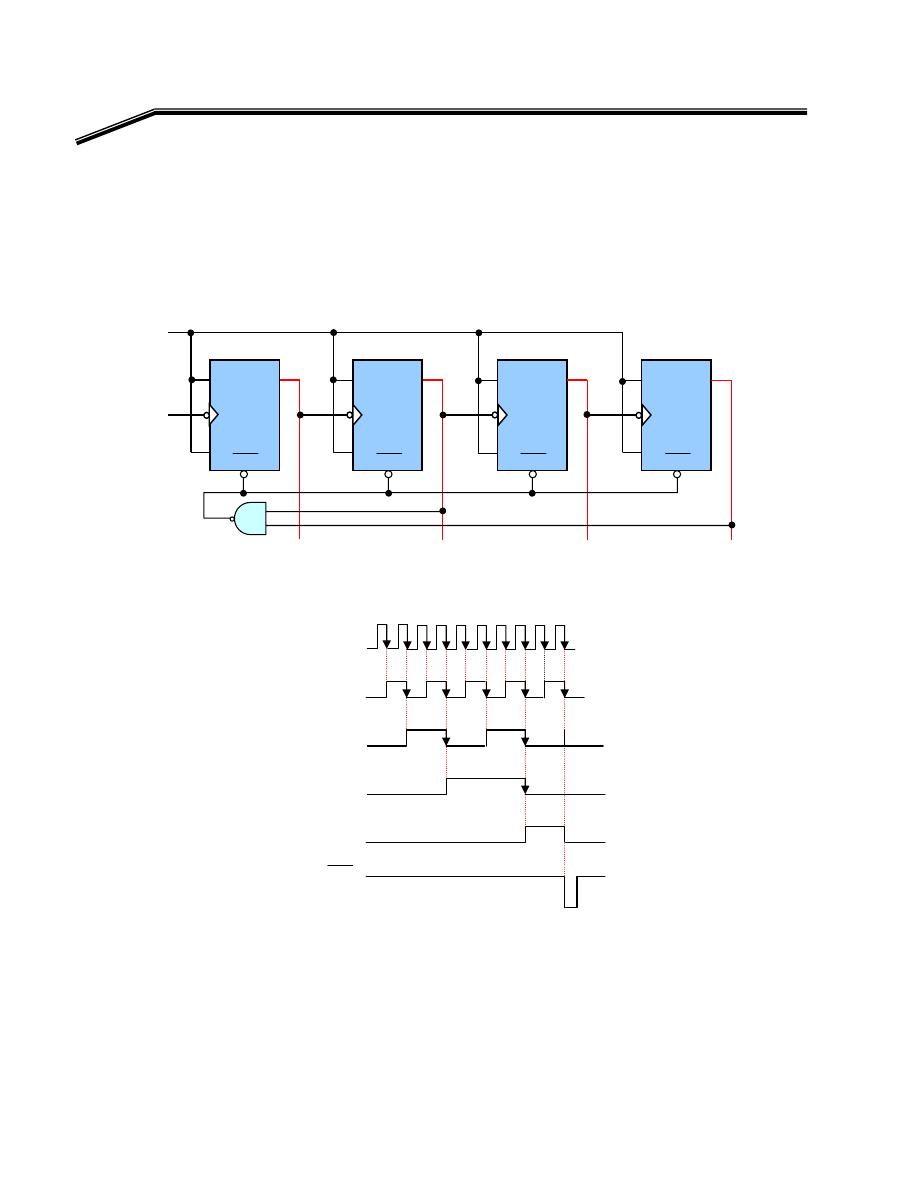

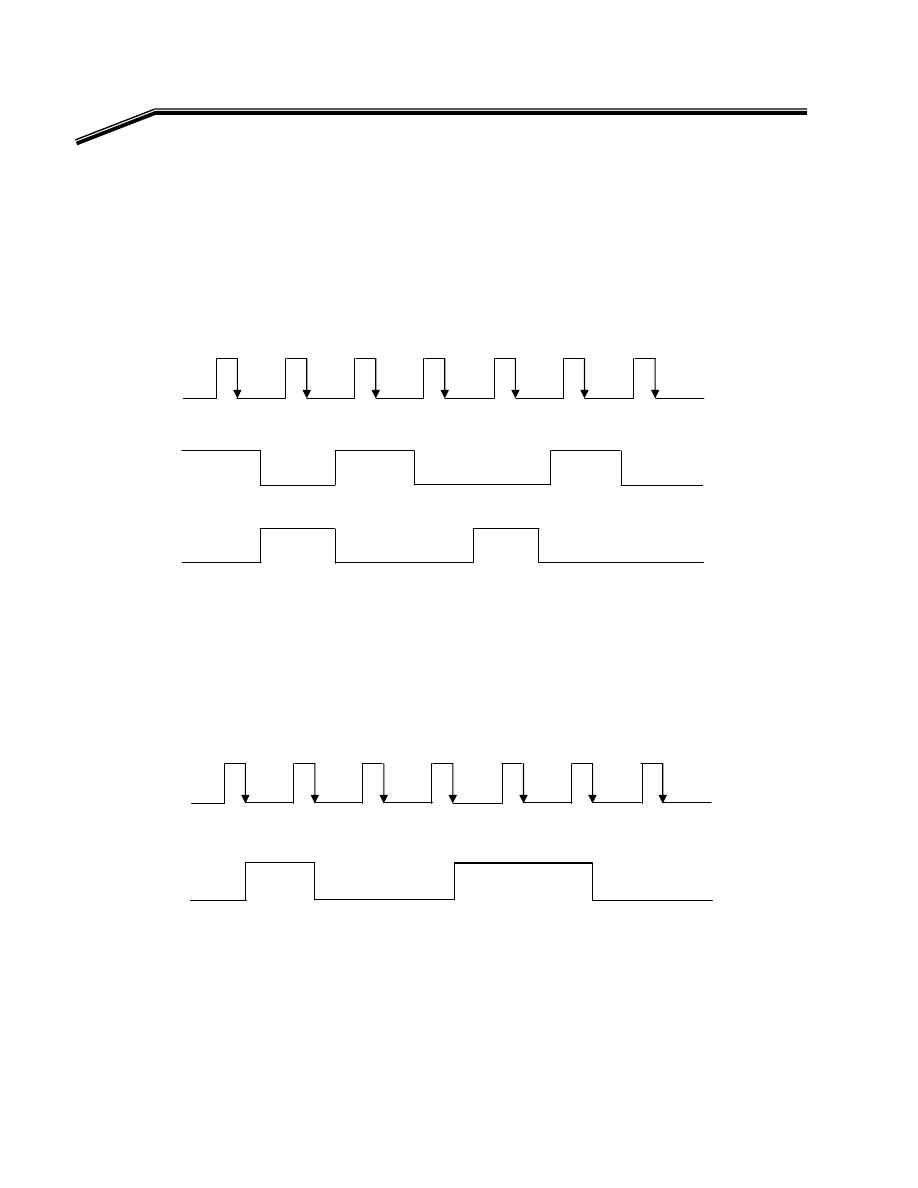

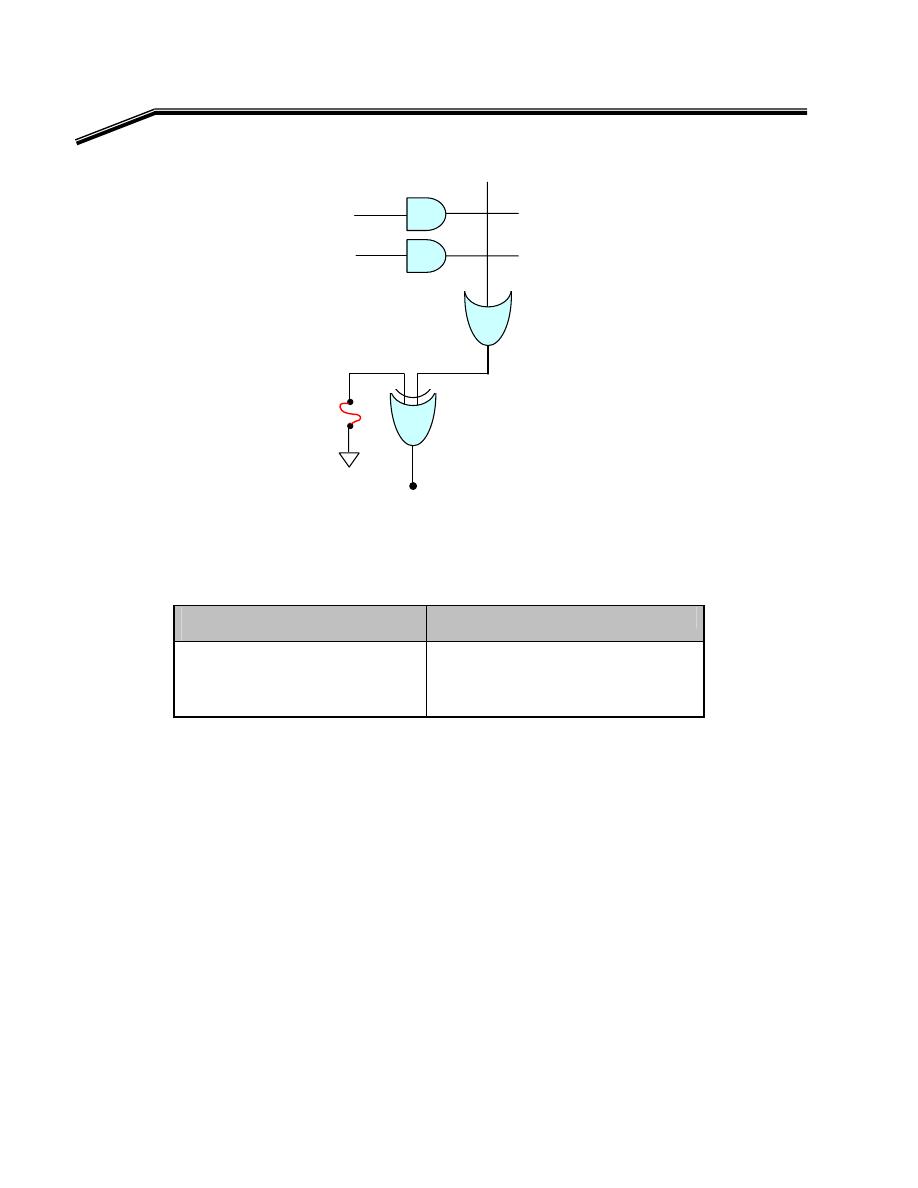

Exclusive-OR Gate

אא

OR

אא

?

?

XOR-gate

،

F

٢

J

٢١

E

אאא

K

אא

XOR

אאא

א

K

א

א

Y

B

A

٠

٠

٠

١

١

٠

١

٠

١

٠

١

١

F

٢

J

٢١

E

אא

XOR

K

F

٢

J

٩

E

אא

XOR

K

אא

XOR

(

)٢ ٩

،

אא

(Y)

(

)١

אא

A

,

B

،

(

)١

א

(

)٠

،א

(

)٠

א

K

אא

XOR

אא

OR

אאא

A = B =

١

אא،

XOR

(

)١

א

(

)١

(

)١

،אא

א

אאאאא

K

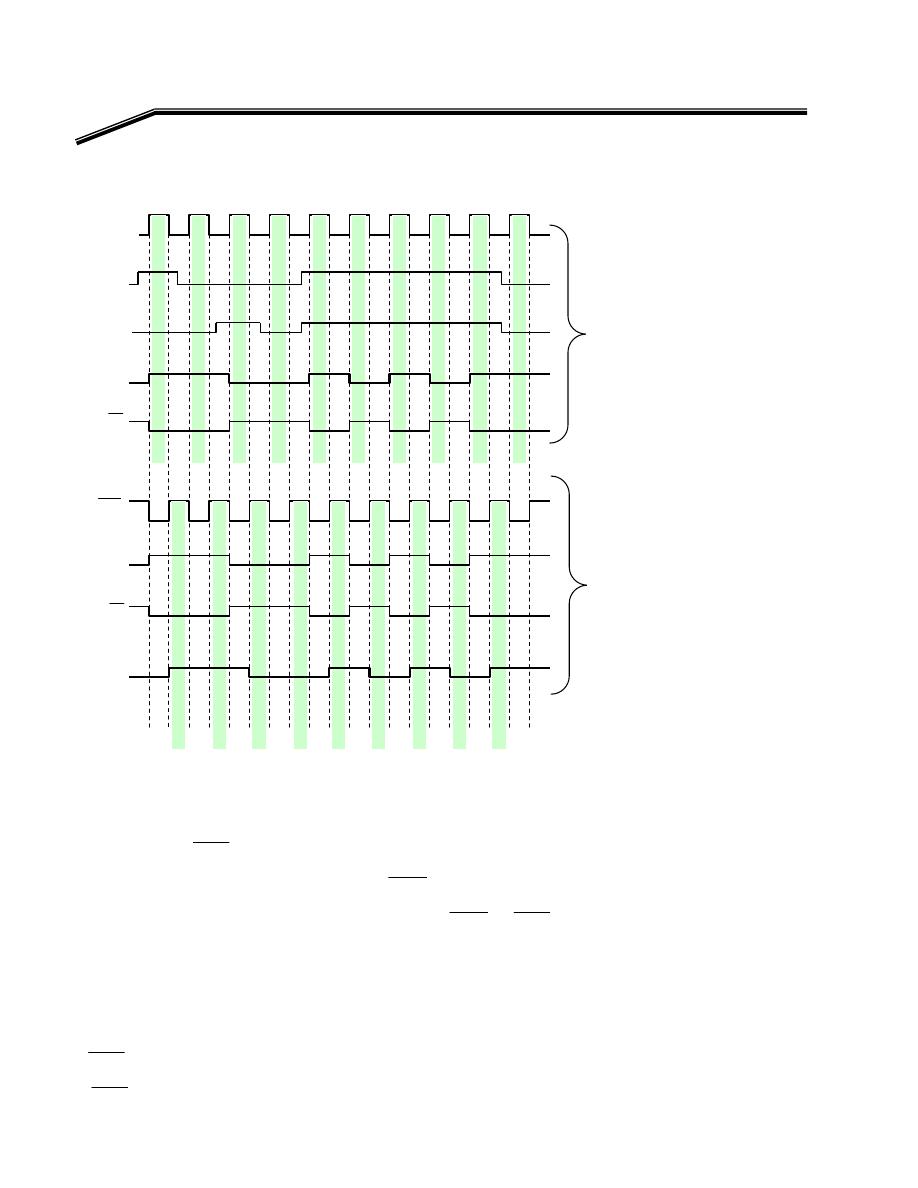

Y

t

٥

t

٤

t

٣

t

٢

t

١

A

B

Y

B

A

אא

٧٤١

א

א

אאאא

א

-

٦٤

-

אאאאאא

W

Y =

B

A

B

A

+

א

א

אא

W

Y = A

⊕ B

א

⊕

A

B

K

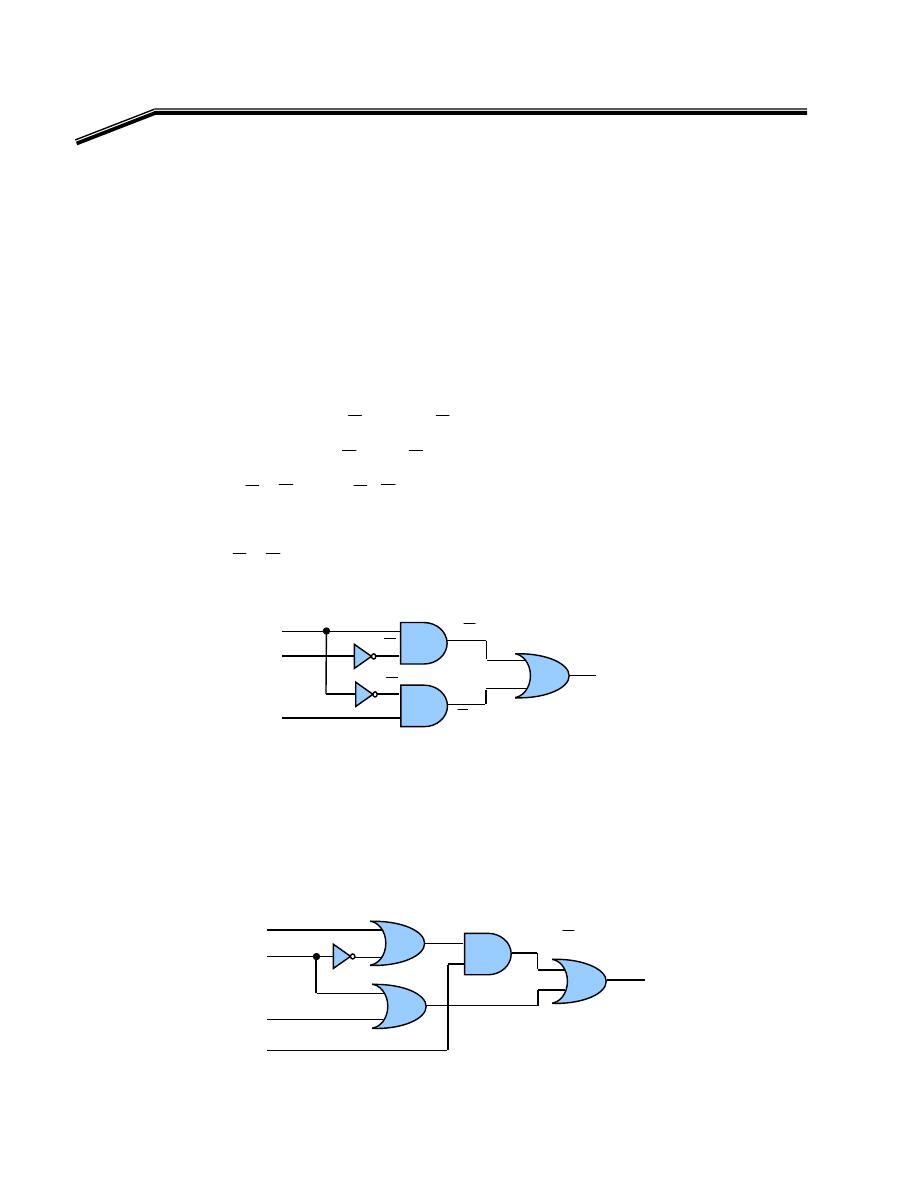

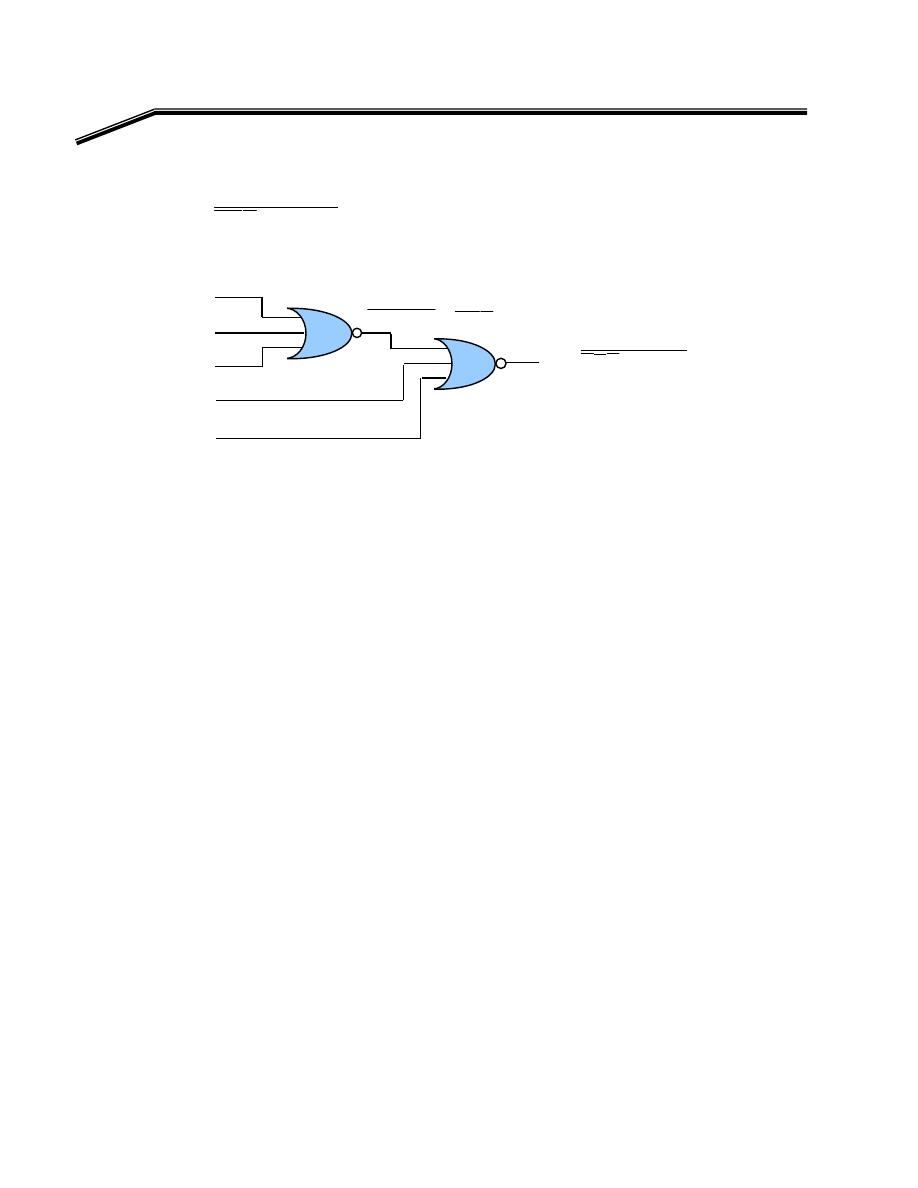

אאאא

XOR

אאאא

AND, OR, NOT

אא،

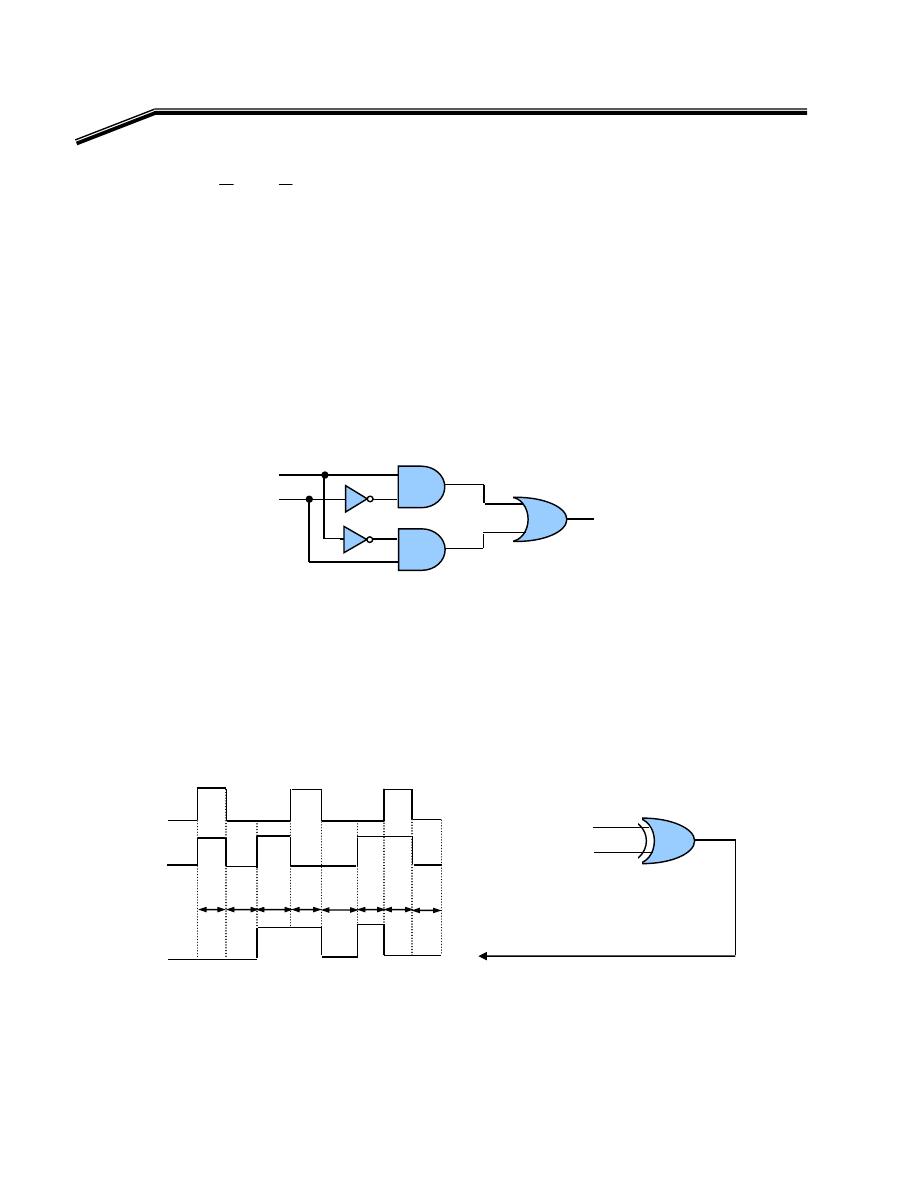

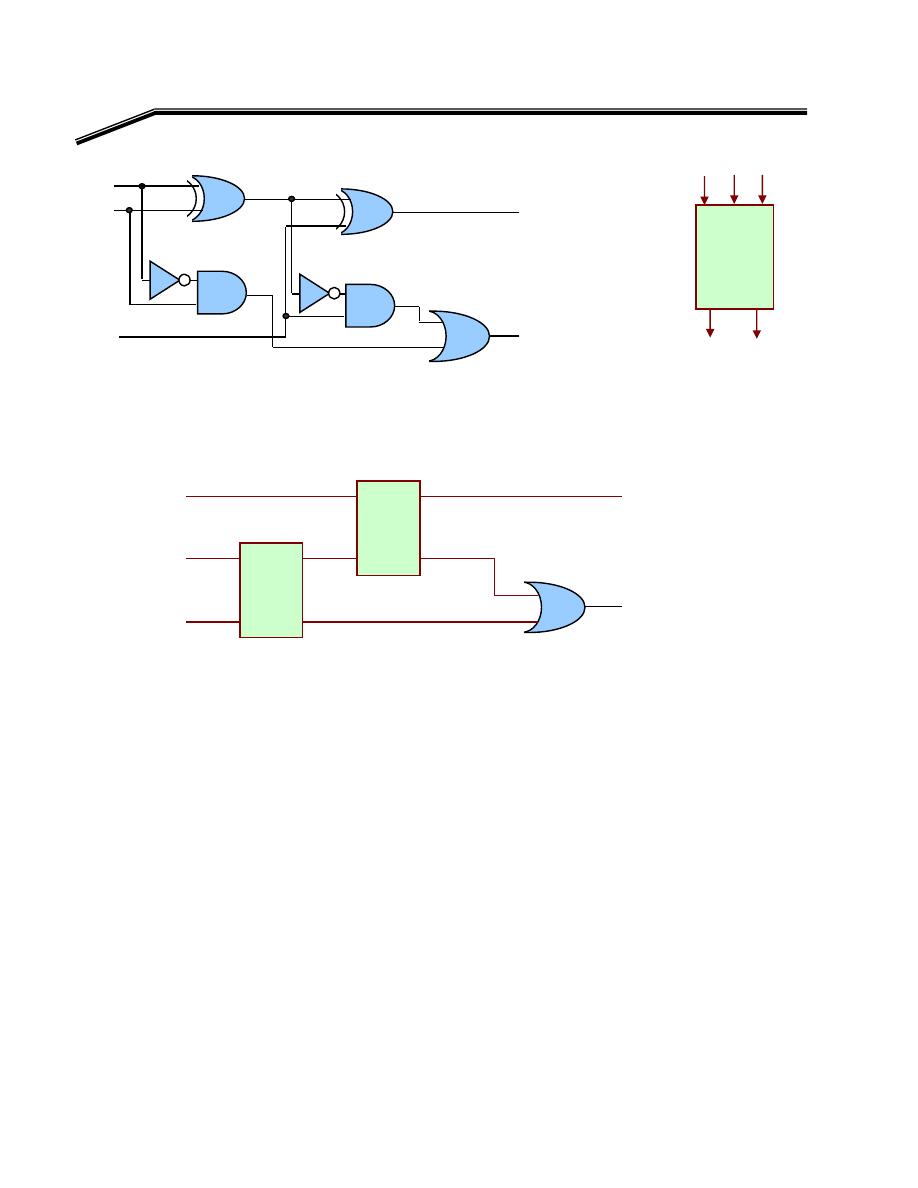

F

٢

J

٣١

E

אא

א

אא

XOR

א

K

F

٢

J

٣١

E

אא

XOR

א

AND, OR, NOT

K

F

٢

J

٤١

E

אא

XOR

א

אאא،א

א

K

F

٢

J

٤١

E

אאא

XOR

K

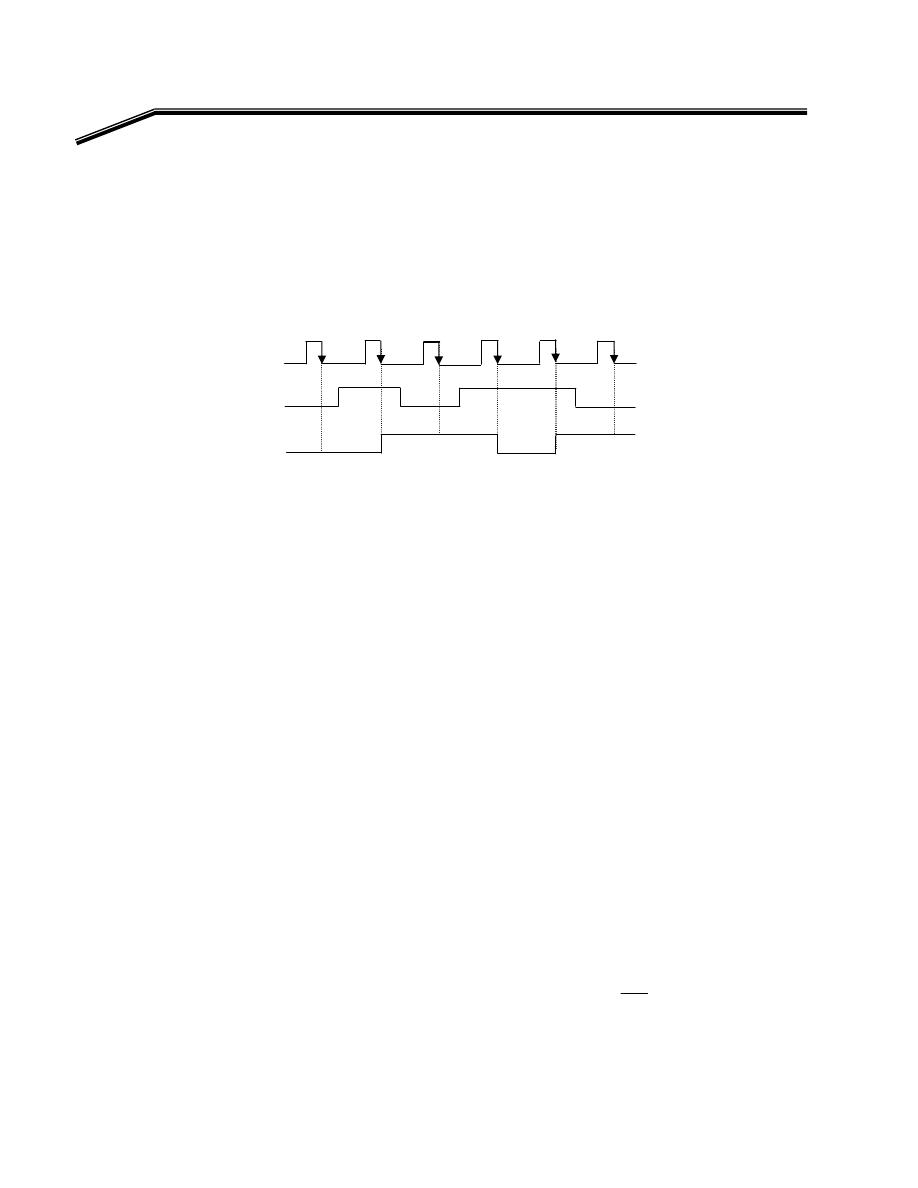

t

٨

t

٧

t

٦

t

٥

t

٤

t

٣

t

٢

t

١

A

B

Y

Y

A

B

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٧٤

-

Y

A

B

٢

J

٩

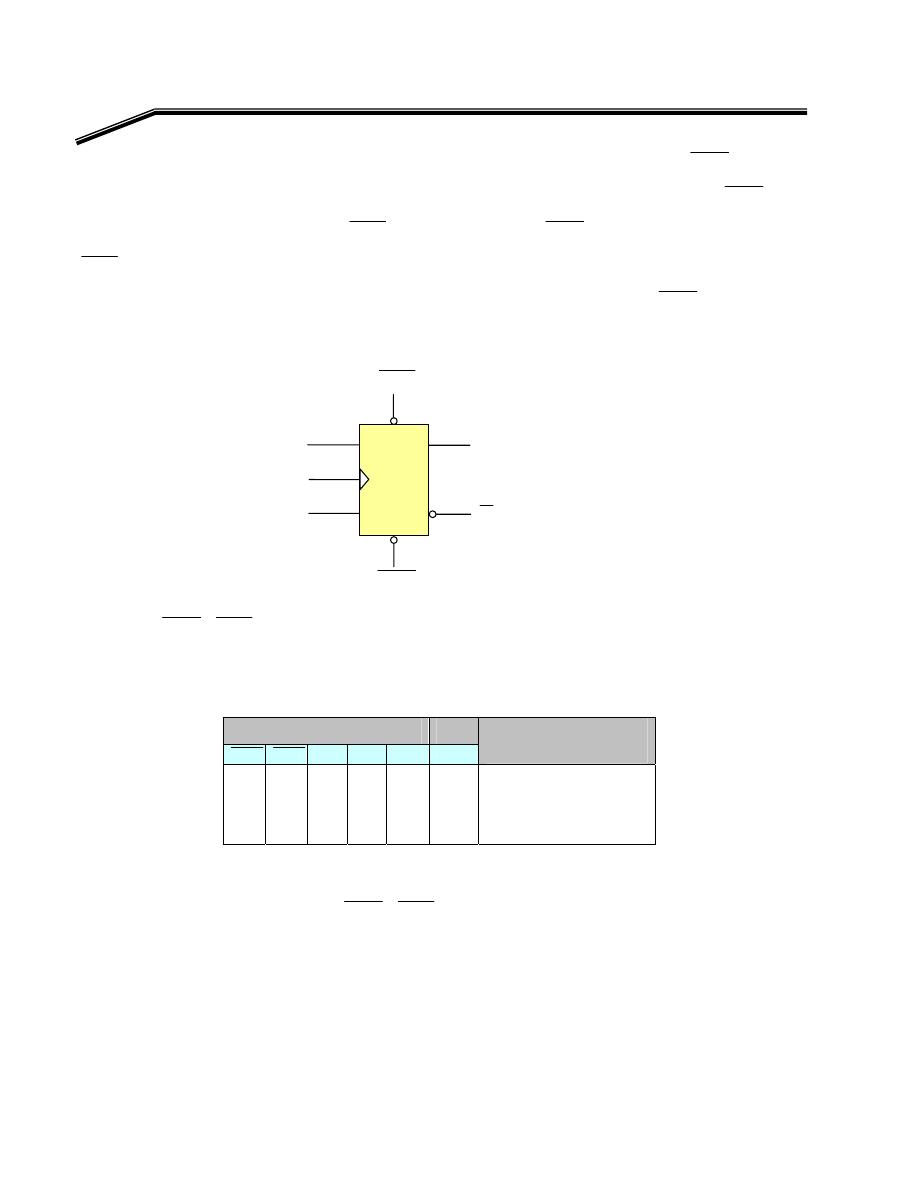

א

NOR

א

F

א

E

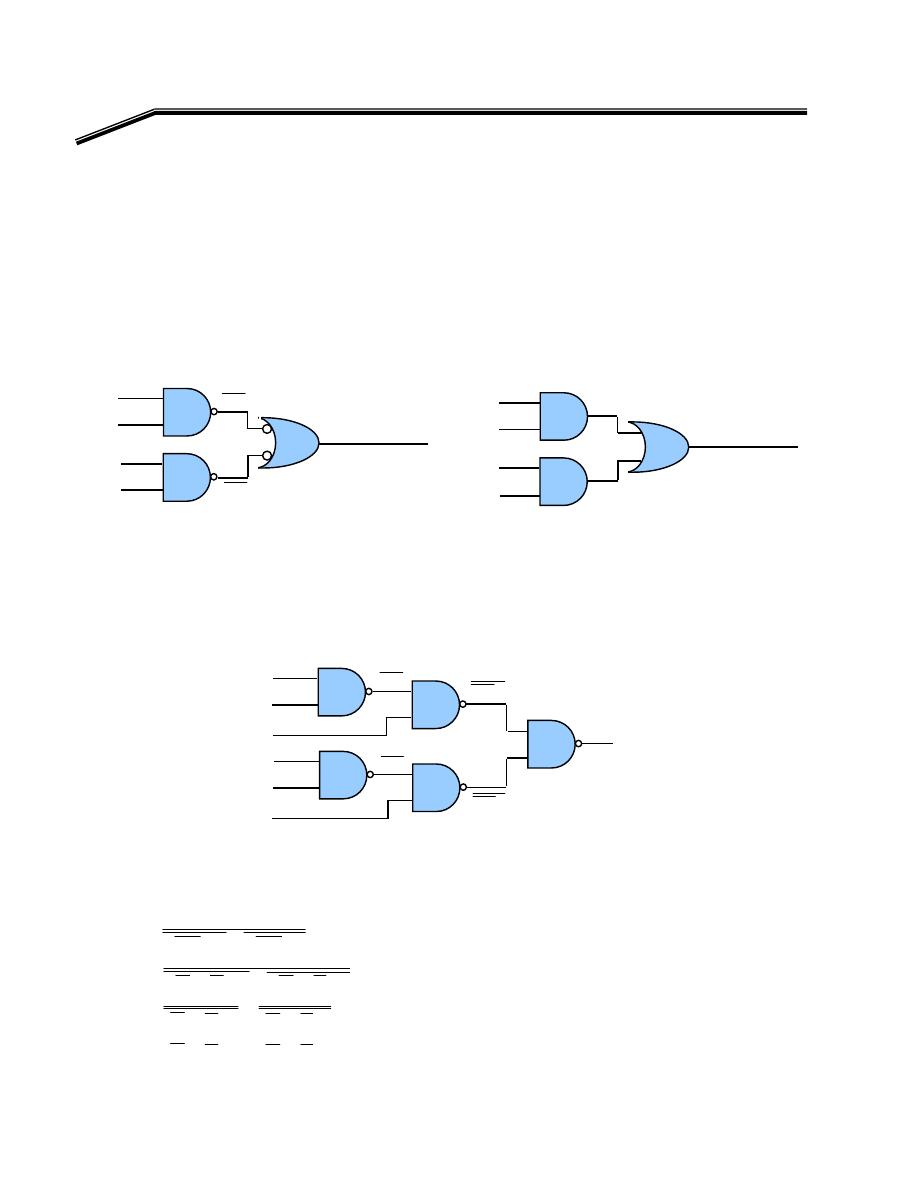

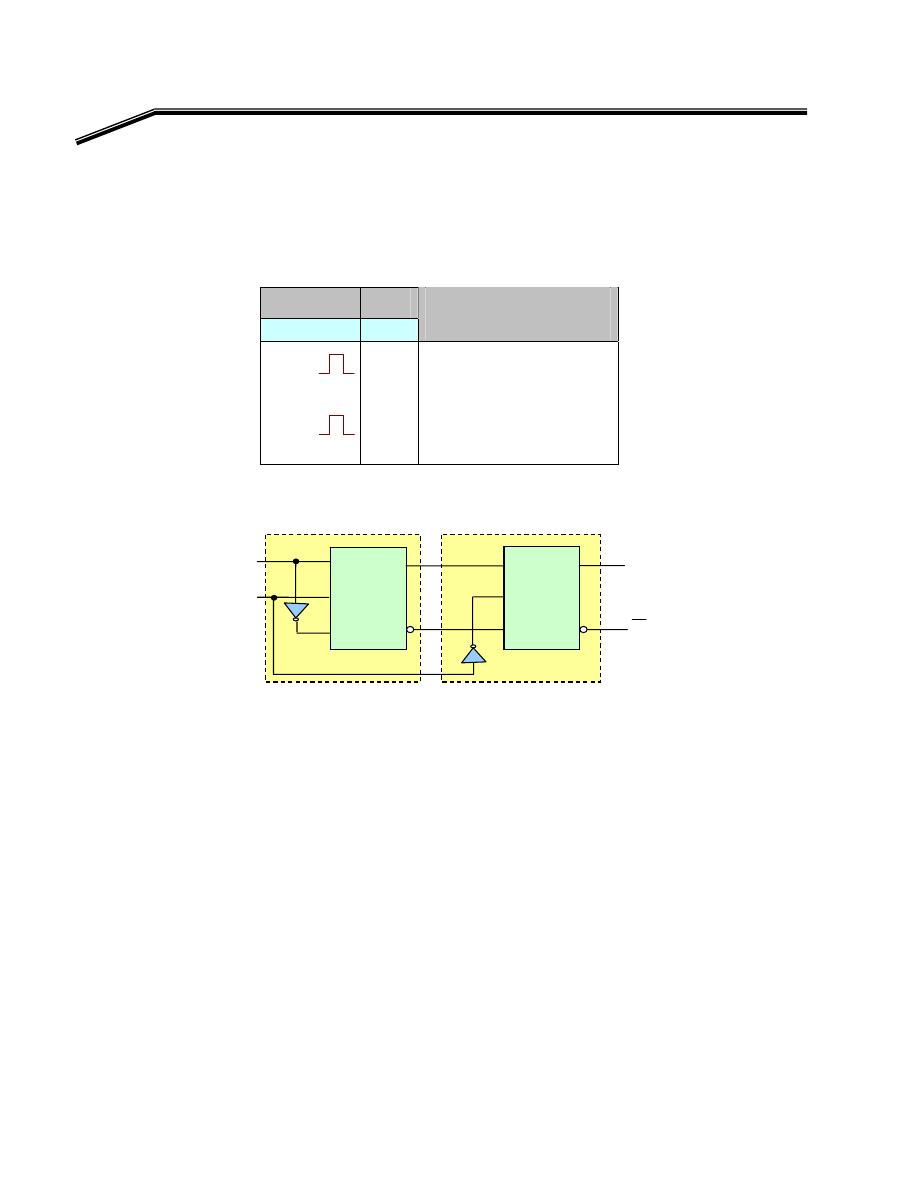

Exclusive-NOR Gate

אא

NOR

א

XNOR-gate

א،

א

אאא

XOR

،

F

٢

J

٥١

E

אאא

K

אא

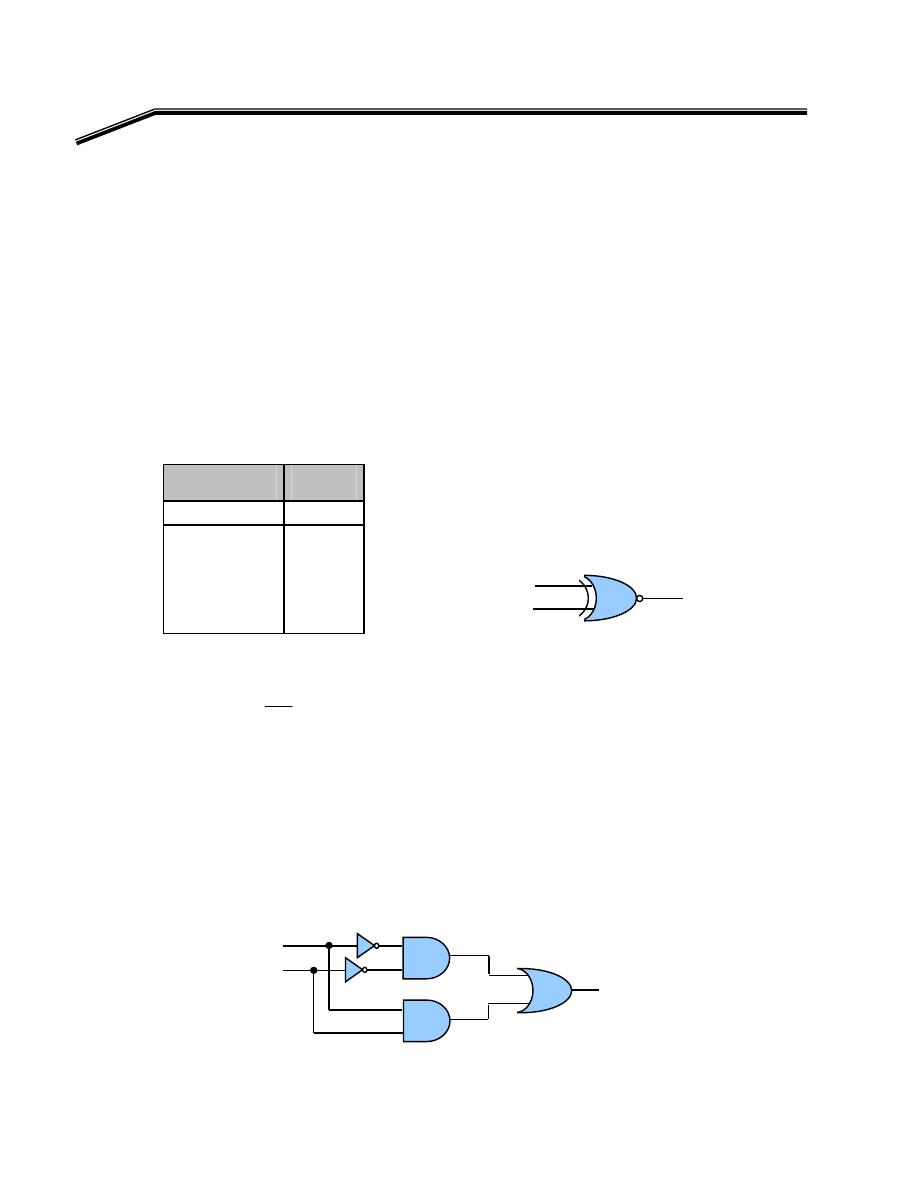

XNOR

F

٢

J

٠١

E

אא،

(Y)

(

)١

אא

A, B

A = B =

٠

A = B =

١

(

)٠

א

(

)١

א

(

)٠

،א

(

)١

א،אא

א

אאאא

K

א

א

Y

B

A

١

٠

٠

٠

١

٠

٠

٠

١

١

١

١

F

٢

J

٥١

E

אא

XNOR

K

F

٢

J

٠١

E

אא

XNOR

K

אאאאאא

W

Y =

B

A

AB

+

אאא

W

Y = A ~ B

א

~

א

K

אאאא

XNOR

אא

אא

AND, OR, NOT

אא،

F

٢

J

٦١

E

אאא

אא

XNOR

א

K

F

٢

J

٦١

E

אא

XNOR

א

AND, OR, NOT

K

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٨٤

-

F

٢

J

٧١

E

א

XNOR

א

A

,

B

،א

אא

XNOR

אא

(Y)

K

F

٢

J

٧١

E

אאא

XNOR

K

٢

J

٠١

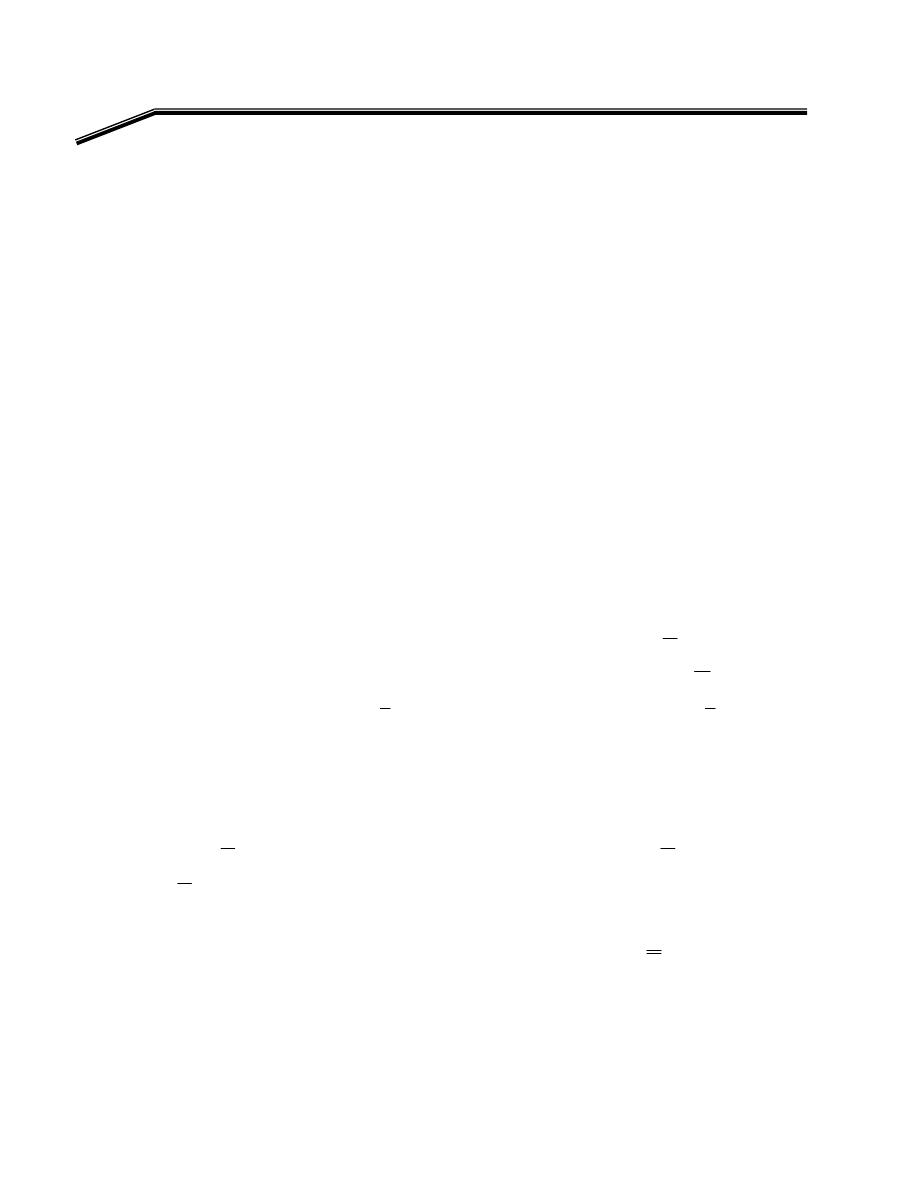

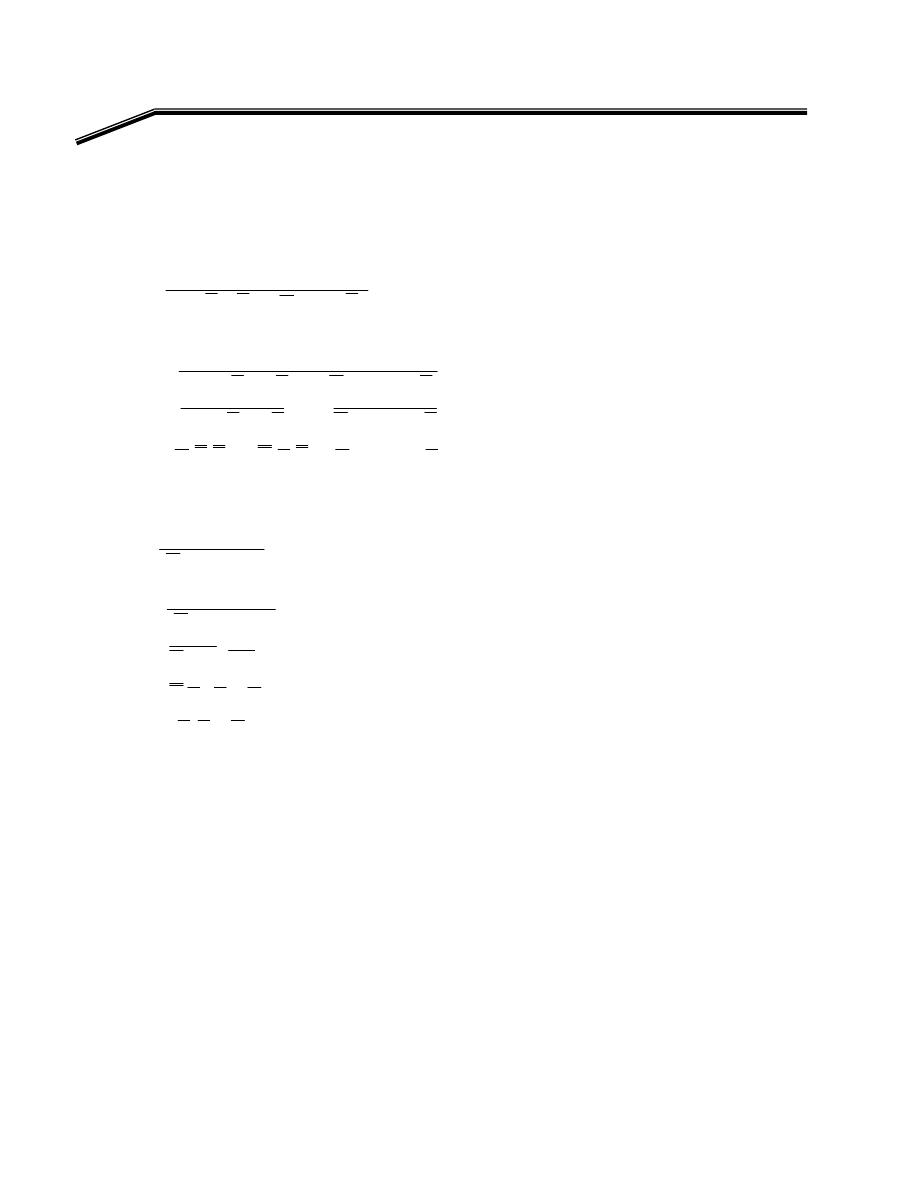

אאא

Rules of Boolean Algebra

F

٢

J

١١

E

אאאא

אאא

א

K

.٢A + ١ = ١

.١A + ٠ = A

.٤A • ١ = A

.٣A • ٠ = ٠

.٦A + A = ١

.٥A + A = A

.٨A • A = ٠

.٧A • A = A

.٠١A + AB = A

.٩A = A

F

٢

J

١١

E

אאאא

K

אאאאאאא

א

K

א

(

١)

:

A +

٠ = A

אאא

א

OR

א

(

)٠

،אא

A

א،

(

)١

(

)٠

K

א

A=

١

א

(

)١

א

A

K

א

A=

٠

א

(

)٠

A

K

א

OR

(

)٠

א

אא

(A +

٠= A)

K

א

(

٢)

:

A +

١ = ١

אאאא

OR

א

(

)١

א

،א

A

א،

(

)١

א

(

)٠

K

(

)١

אא

OR

א

Y

t

٨

t

٧

t

٦

t

٥

t

٤

t

٣

t

٢

t

١

A

B

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٩٤

-

(

)١

אאא

אא

K

א

OR

(

)١

אא

(

)١

(A +

١= ١)

K

א

(

٣)

:

A

• ٠ = ٠

אאאא

AND

א

(

)٠

،אא

A

،

אא

(

)٠

א

אאאא

K

א

AND

(

)٠

אא

(

)٠

(A

• ٠= ٠)

K

א

(

٤)

:

A

• ١ = A

אאאא

AND

א

(

)١

א

،א

A

،

אא

(A)

،

אא

A=

٠

אא

AND

(

)٠

،

אא

A=

١

אא

AND

(

)١

אא

(

)١

K

א

AND

(

)١

א

אא

(A

• ١= A)

K

א

(

٥)

:

A + A = A

אא

אא

OR

א

A

،

אאא

K

אא

A =

٠

٠+ ٠= ٠

אא،

A =

١

א

١+ ١= ١

K

א

(

٦)

:

1

A

A

=

+

א

W

א

A

א

OR

א

A

אאאא

אא

(

)١

K

א

A=

٠

1

1

0

0

0

=

+

=

+

K

א

A =

١

1

0

1

1

1

=

+

=

+

K

א

(

٧)

:

A

• A = A

אא

A

אא

AND

אא

א

K

אא

A =

٠

٠• ٠= ٠

אא،

A =

١

א

١• ١= ١

،

א

אא

AND

א

A

K

א

(

٨)

:

0

A

A

=

•

א

A

א

AND

א

A

אא

אא

אא

(

)٠

،

אאא

A

A

(

)٠

،א

(

)٠

א

AND

אא

(

)٠

K

א

(

٩)

:

A

A

=

אאאא

K

אא

A =

٠

(

)١

،

א

(

)١

(

)٠

אא

K

אא

٧٤١

א

א

אאאא

א

-

٠٥

-

א

(

٠١)

:

אאא

(

)٢

א

(

)٤

W

A + AB = A (

١+ B)

= A (

)١

= A

٢

J

١١

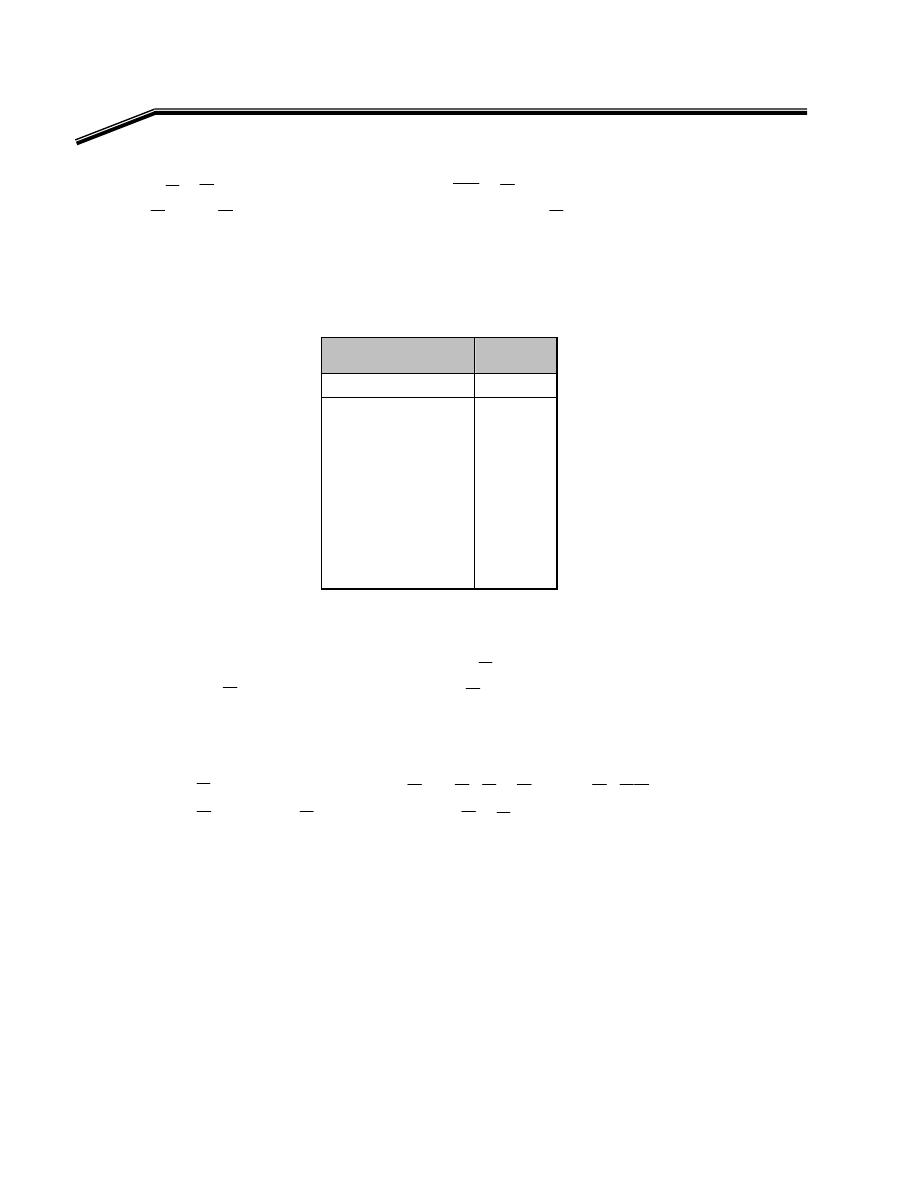

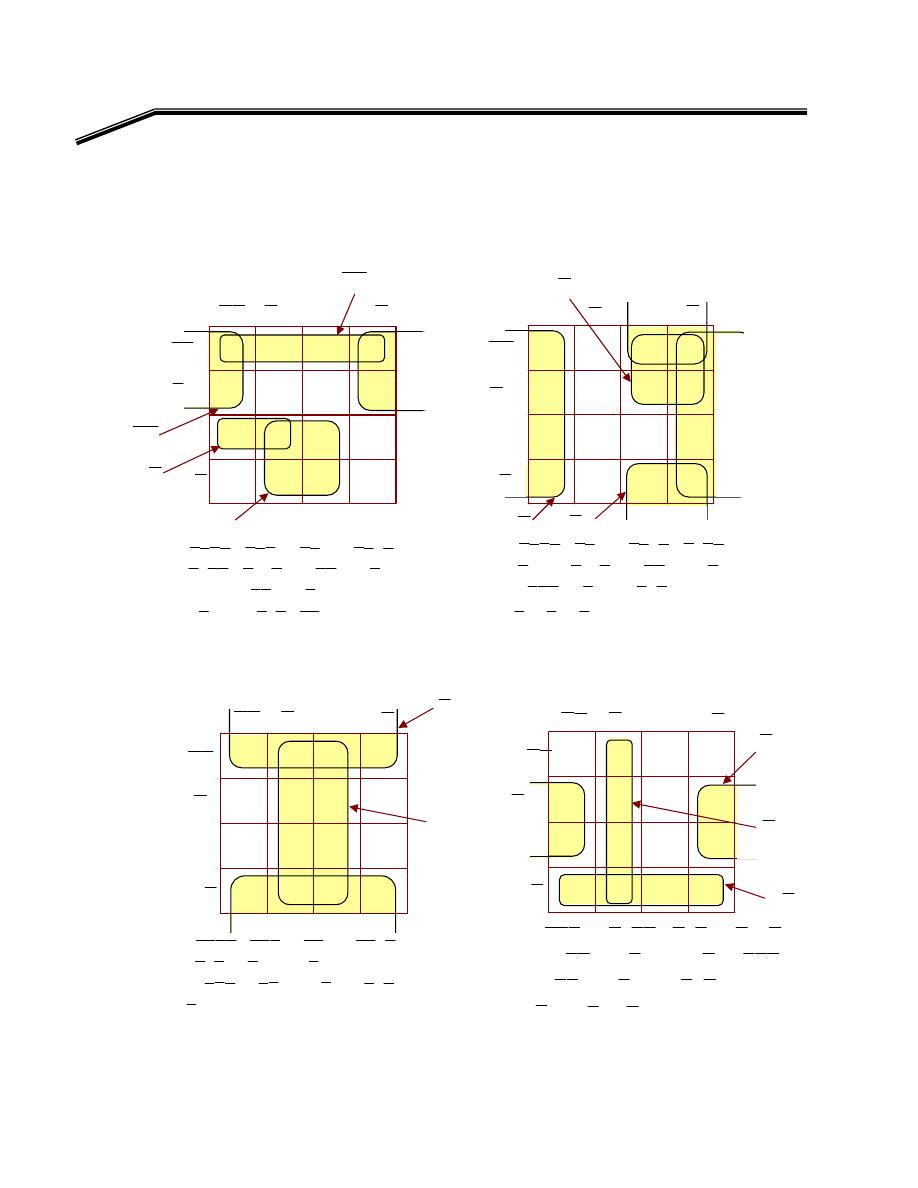

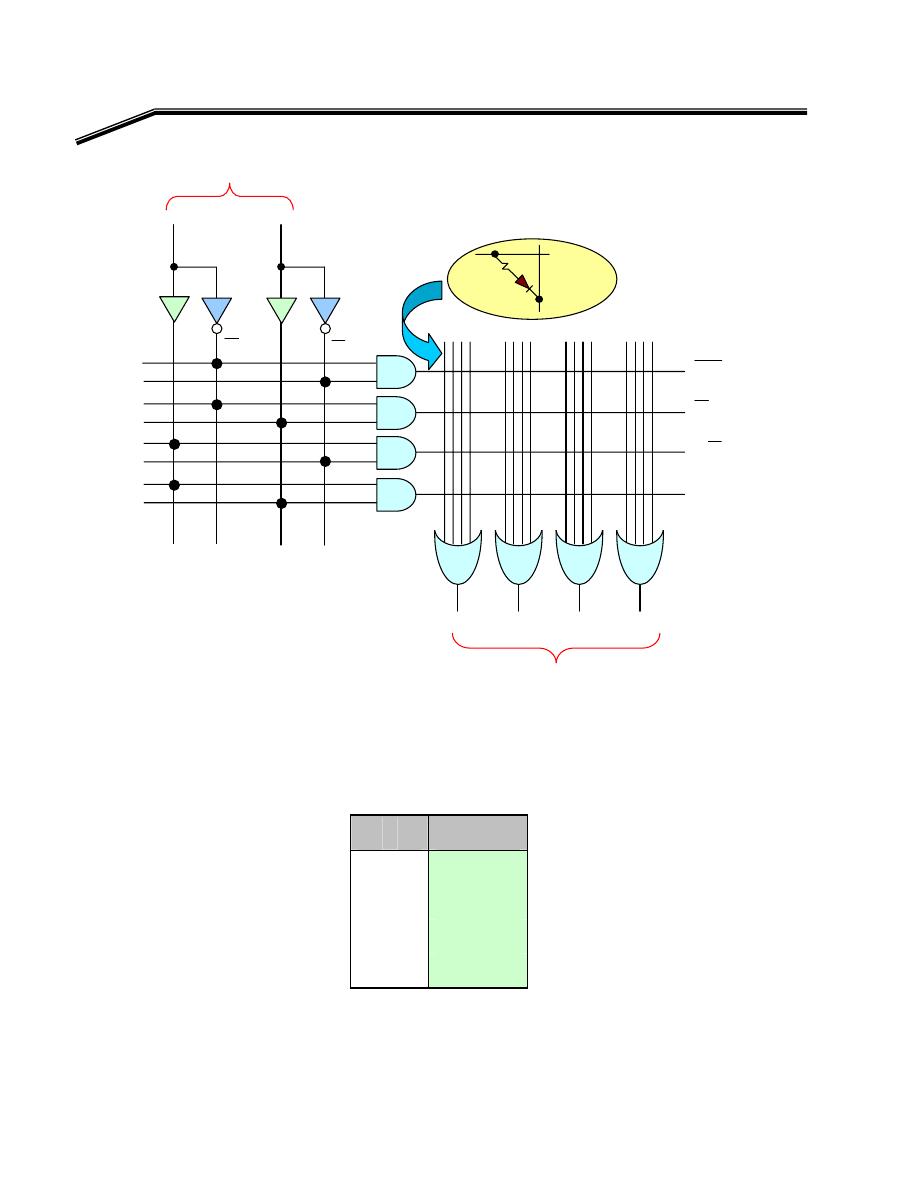

אאא

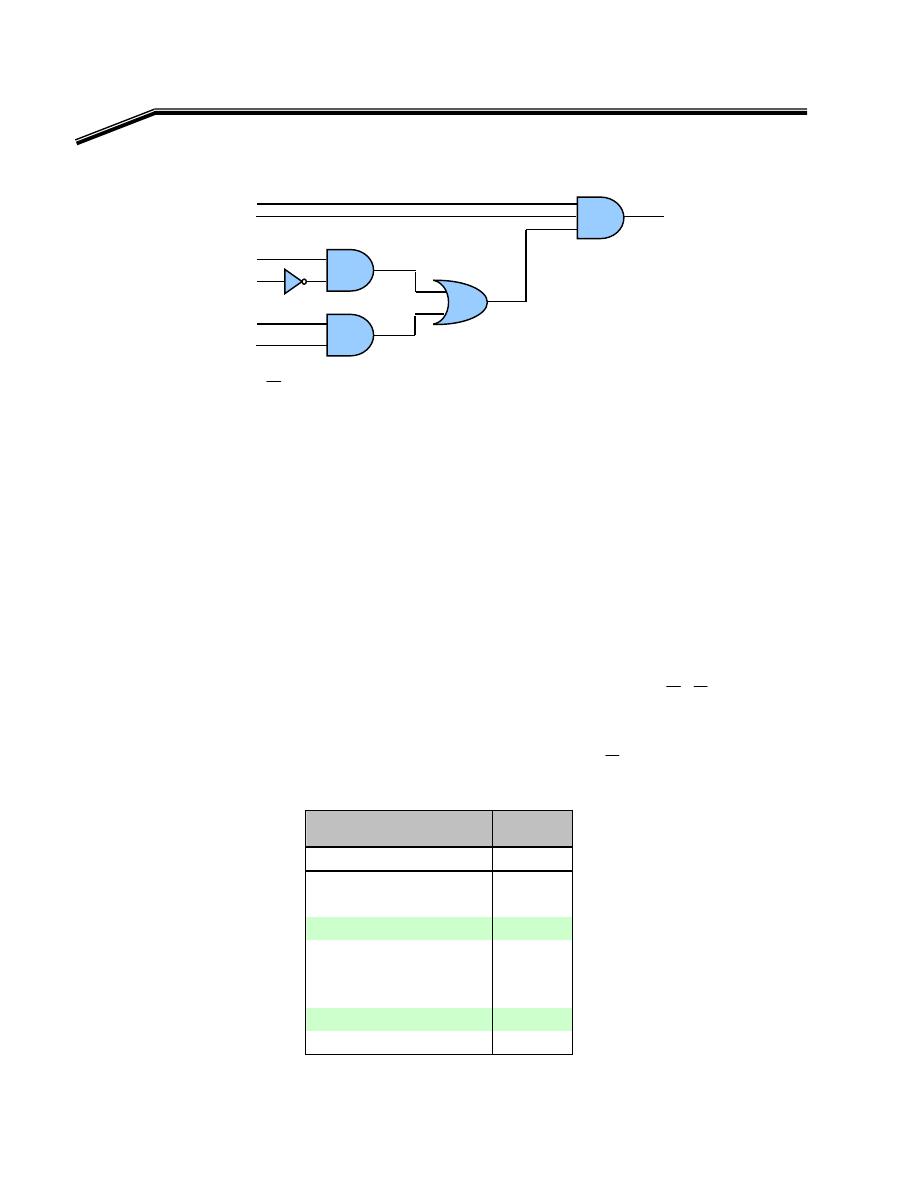

The Boolean Expression for a Logic Circuit

،אאא

אא

אא

אאא

K

אאא،

א

F

٢

J

٨١

E

K

אא

אאא

W

١

K

אאא

AND

אא

B

A,

B

A

K

٢

K

אאא

AND

אא

,C

A

C

A

K

٣

K

אאא

OR

אא

C

A

,

B

A

C

A

B

A

+

K

אאא

W

C

A

B

A

Y

+

=

F

٢

J

٨١

E

אאאא

K

F

٢

J

٢

EW

א

אאאאא

F

٢

J

٩١

E

K

א

W

)

B

A

(

D

+

C

B

+

C

B

+

D

C

Y

A

B

B

A

A

B

C

A

Y

A

B

C

אא

٧٤١

א

א

אאאא

א

-

١٥

-

F

٢

J

٩١

E

אאא

F

٢

J

٢

E

אאא

K

אאאאא

W

)

C

B

(

)

B

A

(

D

Y

+

+

+

=

٢

J

٢١

א

אאא

Implementation of a Logic Circuit Using a Boolean Expression

אאאא

אא

K

אאאא

W

)

EF

D

C

(

AB

Y

+

=

אאאאא

A

,

B

)

EF

D

C

(

+

א

AND

א،

)

EF

D

C

(

+

D

,

C

א

AND

،

E,F

א

AND

אא،

AND

א

OR

K

אא

W

)

EF

D

C

(

B

A

Y

+

=

אאאאא

)

EF

D

C

(

+

؛

א

אאאא

EF

,

D

C

אא؛

D

אאא،

K

אאאאאא

)

EF

D

C

(

AB

+

W

١

K

א

NOT

א

D

K

٢

K

א

AND

א

EF

,

D

C

K

٣

K

א

OR

אא

)

EF

D

C

(

+

K

٤

K

א

AND

אא

Y

K

AND

AND

OR

NOT

אא

٧٤١

א

א

אאאא

א

-

٢٥

-

אאאאאאא

F

٢

J

٠٢

KE

F

٢

J

٠٢

E

אאאא

EF)

D

AB(C

+

K

٢

J

٣١

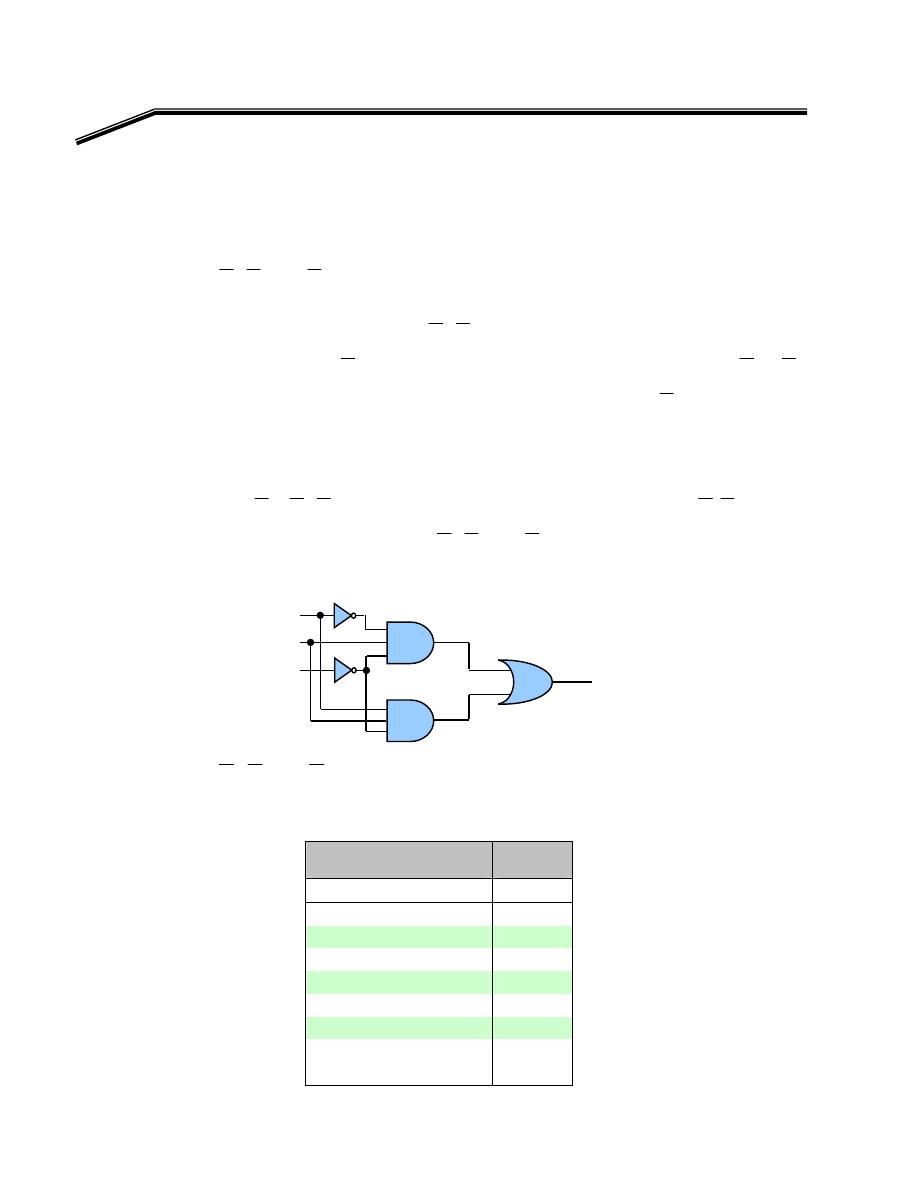

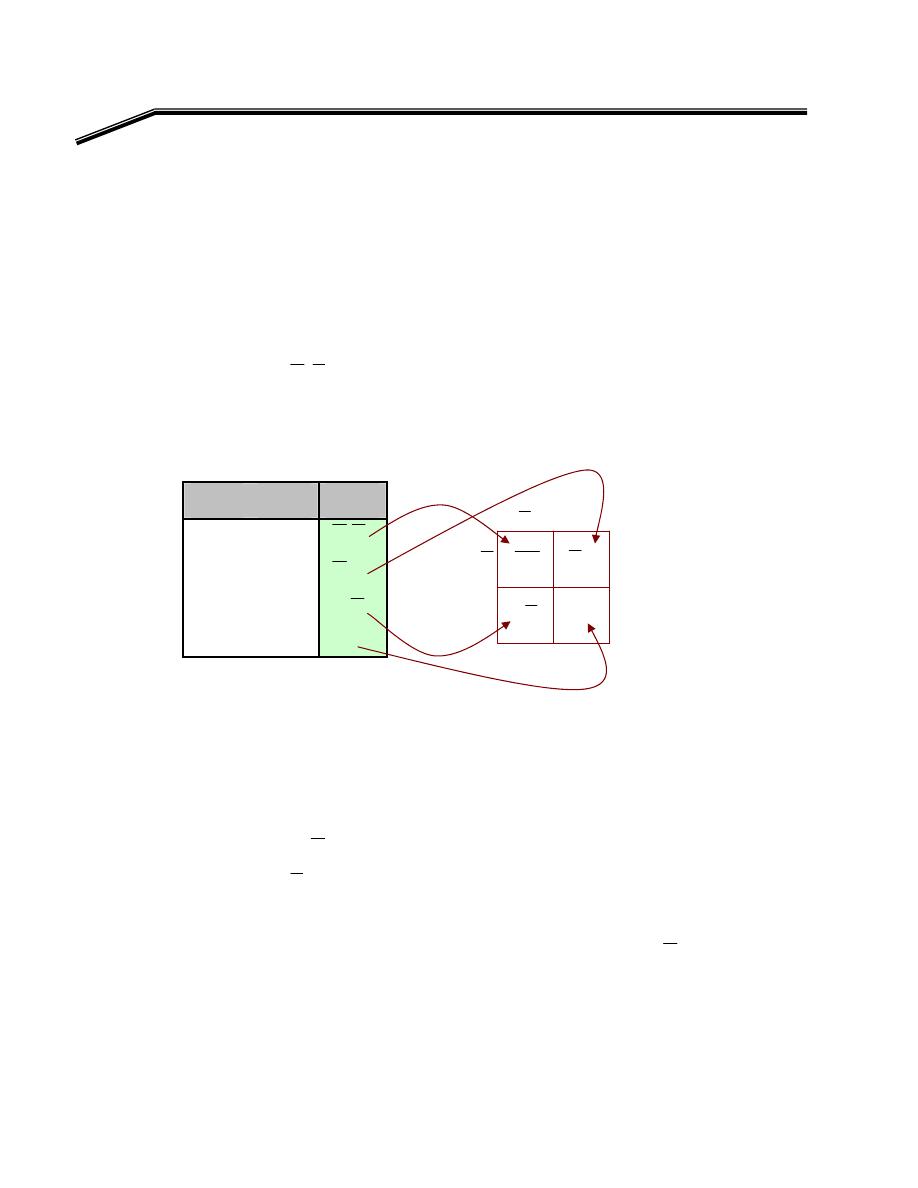

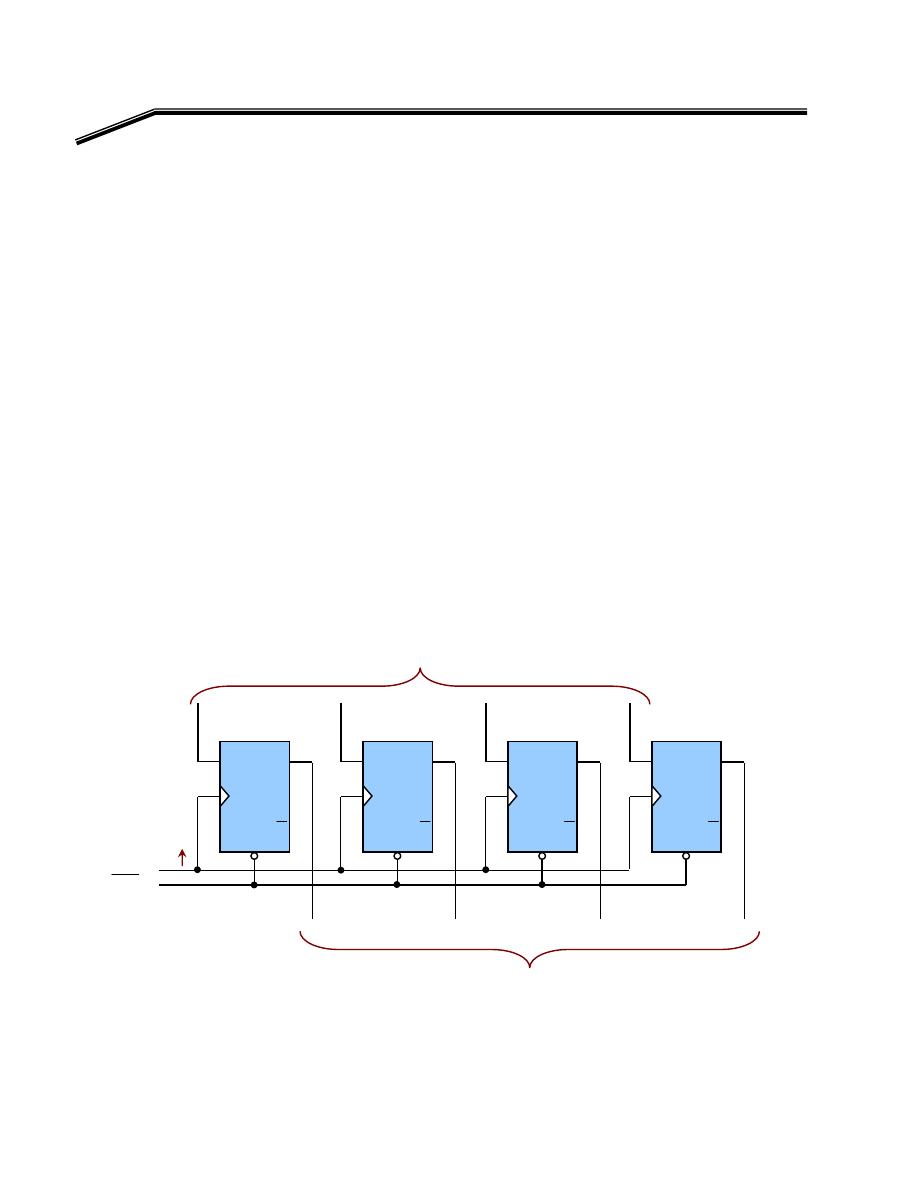

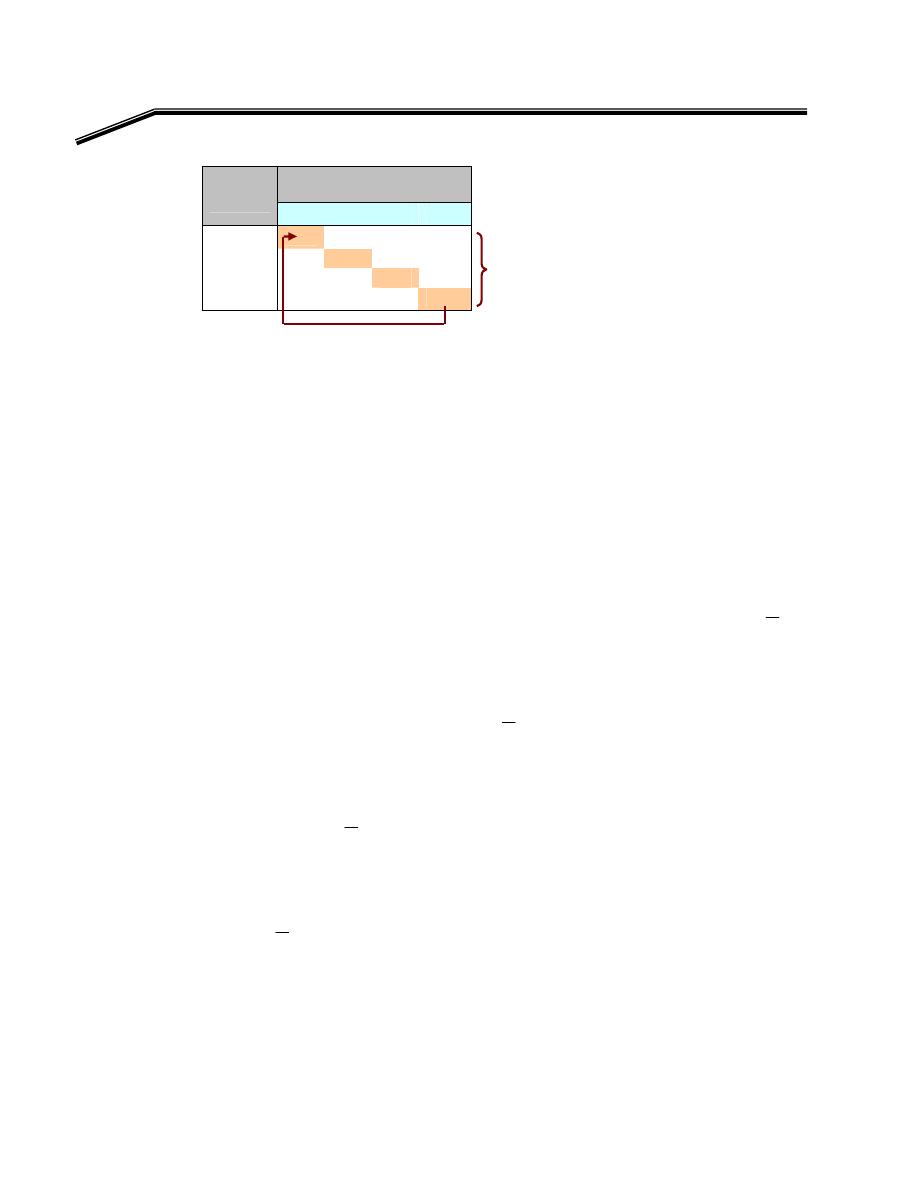

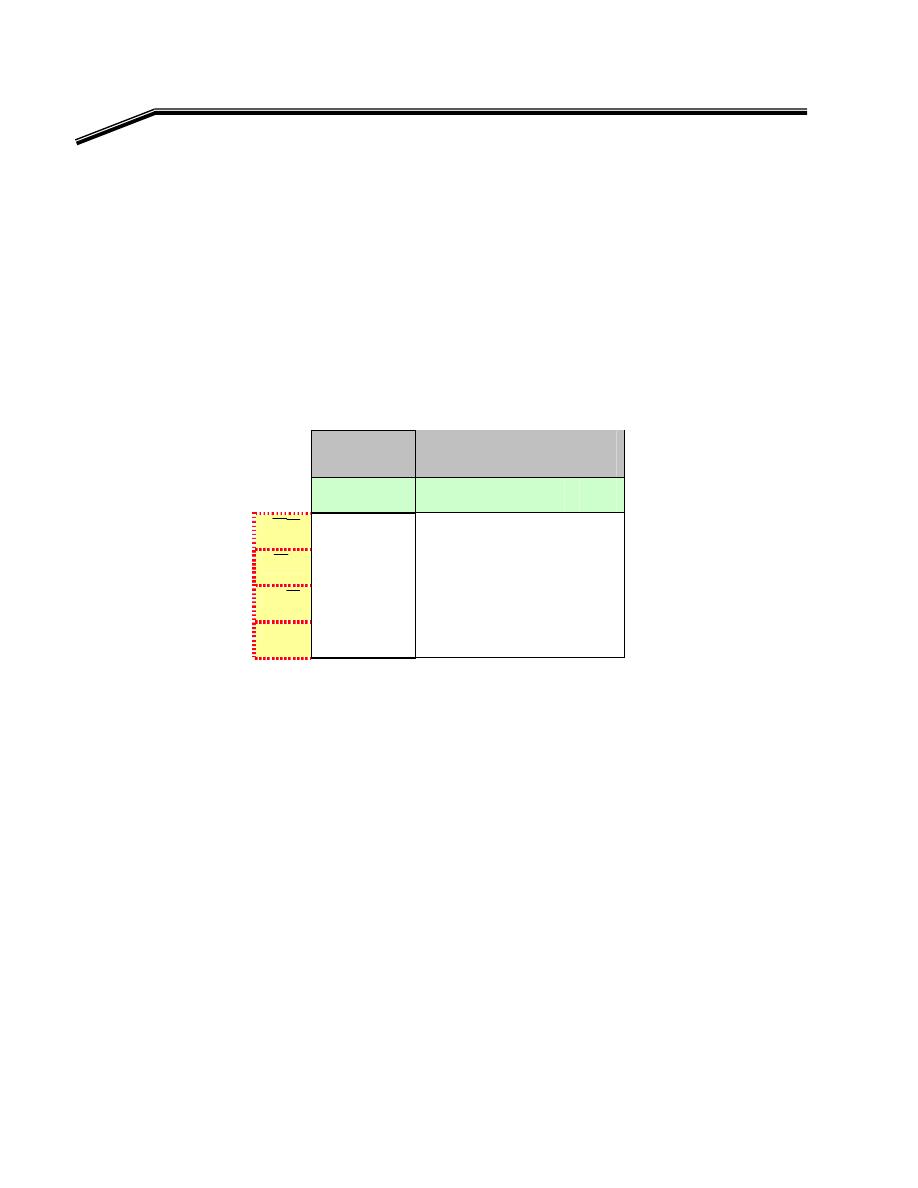

אא

Implementation of a Logic Circuit via a Truth Table

אאאאא

אאאאא،אא

א

K

F

٢

J

٢١

E

אא،אא

אאא

אא

K

אאאא

W

١K

אאאא

Y =

١

אאא،

א

Y =

١

א

A

=

٠, B = ١, C = ٠

،

א

א

C

B

A

אא

(

)١

א،

(

)٠

،

א

(

)١

אאאא

אא

C

AB

K

א

א

Y

C

B

A

٠

٠

٠

٠

٠

١

٠

٠

١

٠

١

٠

٠

١

١

٠

٠

٠

٠

١

٠

١

٠

١

١

٠

١

١

٠

١

١

١

F

٢

J

٢١

E

אאא

K

A

B

D

C

E

F

Y

אא

٧٤١

א

א

אאאא

א

-

٣٥

-

٢K

אאאאא

Y =

١

א

OR

W

C

AB

C

B

A

Y

+

=

אא

אאא

C

B

A

אאא

C

,

B

,

A

א

AND

אאאא،

C

AB

אאא

C

,

B

,

A

א

AND

אאאא،

OR

אאא

Y

K

אאאאאאא

W

א

NOT

א

C

,

A

א؛

AND

א

א

C

B

A

،

C

AB

א،

OR

אאא

C

AB

C

B

A

+

אאאאאאא،

F

٢

J

١٢

E

K

F

٢

J

١٢

E

אאא

א

C

AB

C

B

A

+

K

F

٢

J

٣

EW

אאאאאאא

F

٢

J

٣١

KE

א

א

Y

C

B

A

٠

٠

٠

٠

١

١

٠

٠

٠

٠

١

٠

١

١

١

٠

٠

٠

٠

١

١

١

٠

١

٠

٠

١

١

٠

١

١

١

C

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٤٥

-

F

٢

J

٣١

E

אאא

אא

K

א

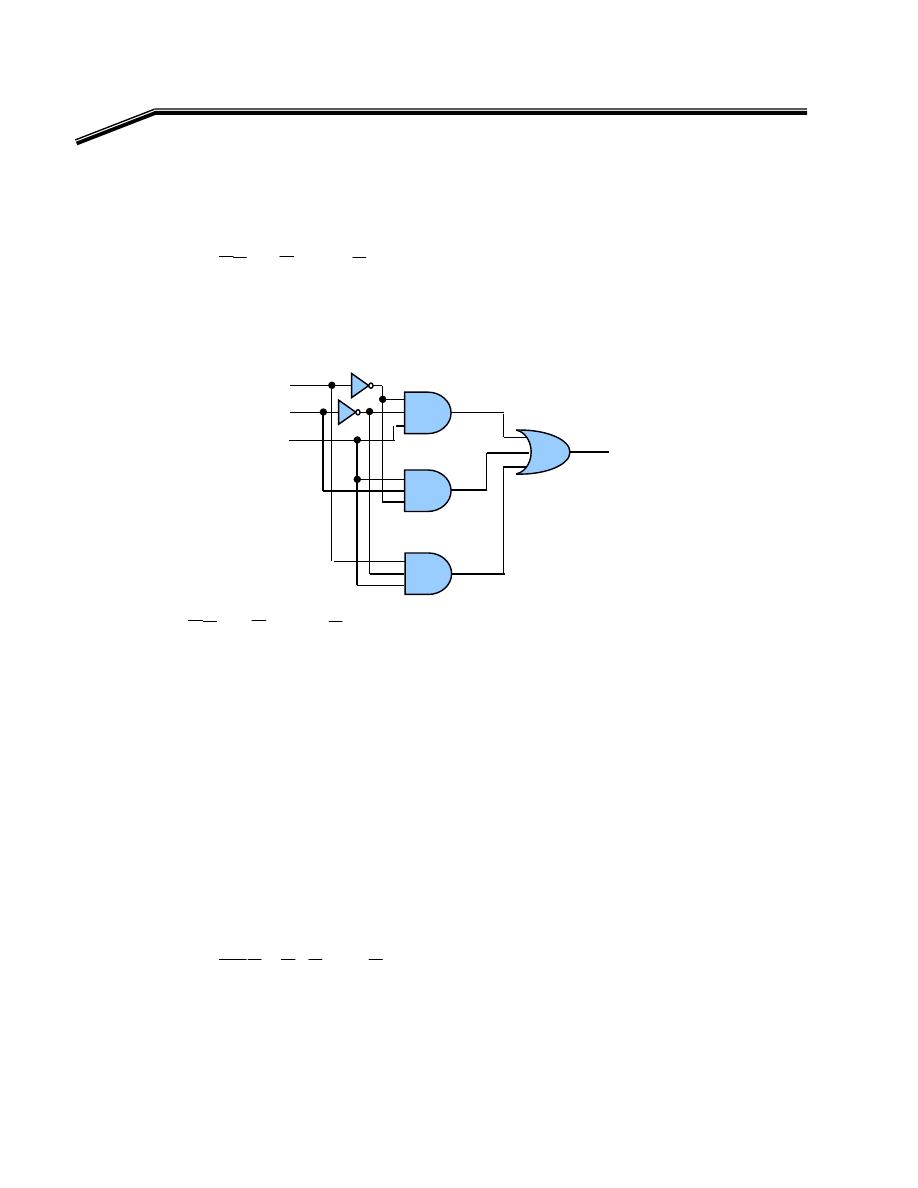

W

אאאאאאא

Y =

١

F

אא

E

א

OR

W

C

B

A

BC

A

C

B

A

Y

+

+

=

אאא

F

٢

J

٢٢

E

K

F

٢

J

٢٢

E

אאאא

C

B

A

BC

A

C

B

A

+

+

K

٢

J

٤١

אאא

Converting a Boolean Expression to a Truth Table

אאאאא

א

(

١or ٠)

K

،אא

(

٢

٢

=

)٤

،

،אא

(

٢

٣

=

)٨

،

א

K

אאא،אא

א

אא

(

)١

א

(Y)

،אא

(

)٠

אא،אא

K

F

٢

J

٤

WE

אאא

W

ABC

C

AB

C

B

A

C

B

A

Y

+

+

+

=

B

A

C

Y

אא

٧٤١

א

א

אאאא

א

-

٥٥

-

א

W

א

(A, B, C)

א،אאא

אאאאא

F

٢

J

٤١

E

K

אאאאאא

W

111

ABC

,

110

C

AB

,

010

C

B

A

,

000

C

B

A

=

=

=

=

אא

(

)١

א

(Y)

،

אאא

(

)٠

א

(Y)

K

א

א

Y

C

B

A

١

٠

٠

٠

٠

١

٠

٠

١

٠

١

٠

٠

١

١

٠

٠

٠

٠

١

٠

١

٠

١

١

٠

١

١

١

١

١

١

F

٢

J

٤١

E

אא

ABC

C

AB

C

B

A

C

B

A

Y

+

+

+

=

K

٢

J

٥١

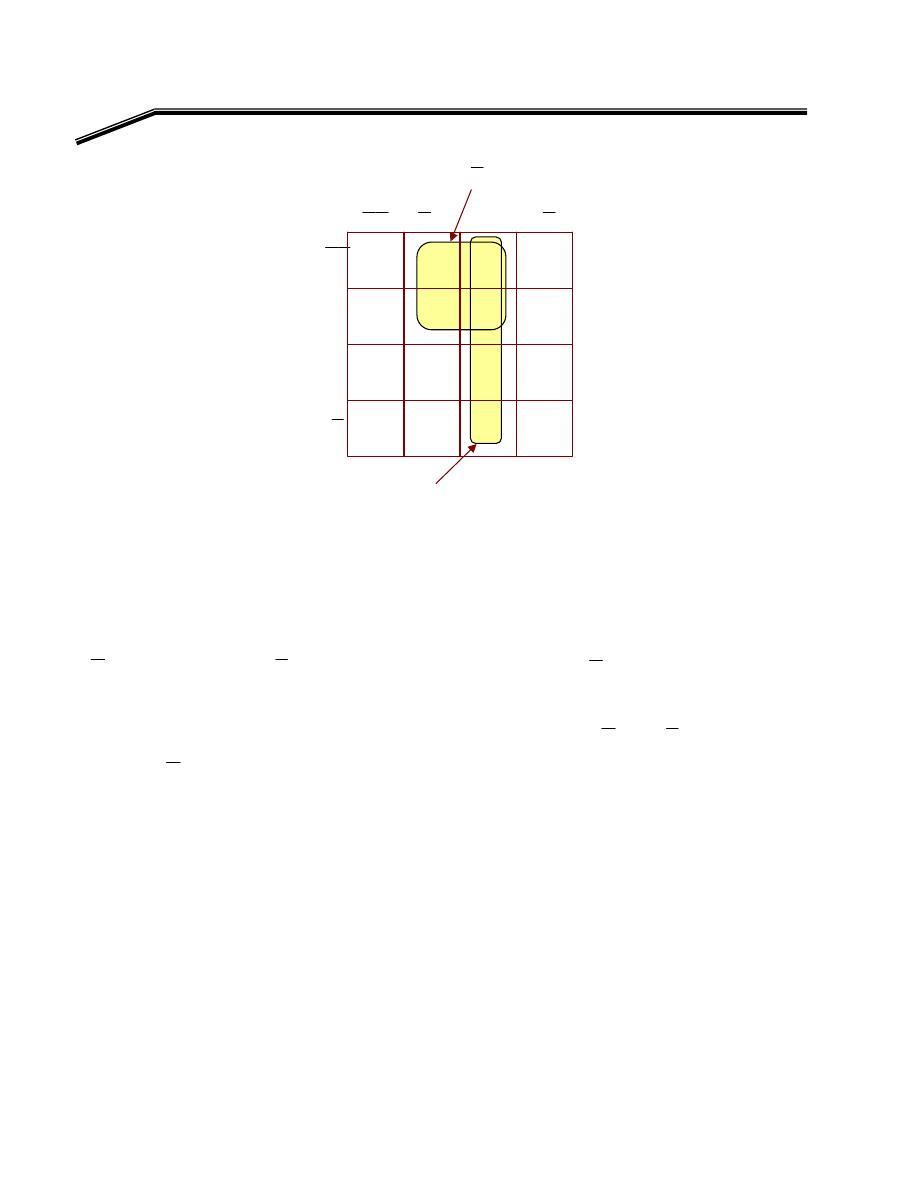

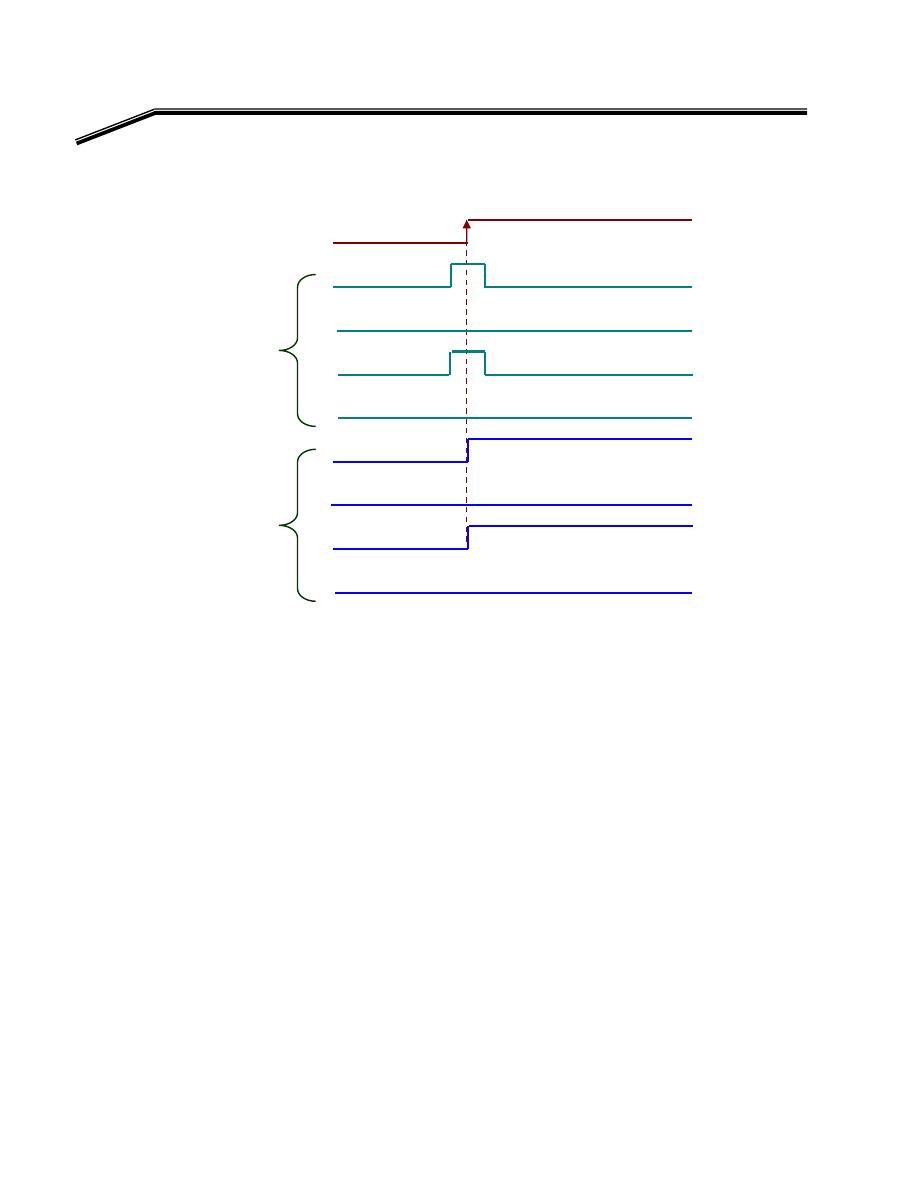

אאאאאא

Simplification of Boolean Expressions Using Boolean algebra

אאאאאאא

F

אאא

E

،א،אאא

א،א،אאא

אאא

K

F

٢

J

٥

WE

א

אאאאאאא

W

)

C

A

(

B

)

C

A

(

A

AB

Y

+

+

+

+

=

א

W

אאאאאאא

W

BC

AB

AC

AA

AB

Y

+

+

+

+

=

אא

٧٤١

א

א

אאאא

א

-

٦٥

-

א

AA

A

F

אא

٧

אאא

E

אא

W

BC

AB

AC

A

AB

Y

+

+

+

+

=

א

٥

A + A = A

،

AB + AB = AB

אא،

W

BC

AC

A

AB

Y

+

+

+

=

א

A

אאאא

W

BC

)

C

1

B

(

A

Y

+

+

+

=

א

٢

A +

١= ١

،

W

Y = A

• ١+ BC

אא

٤

A

• ١= A

،

W

Y = A + BC

א

אא

K

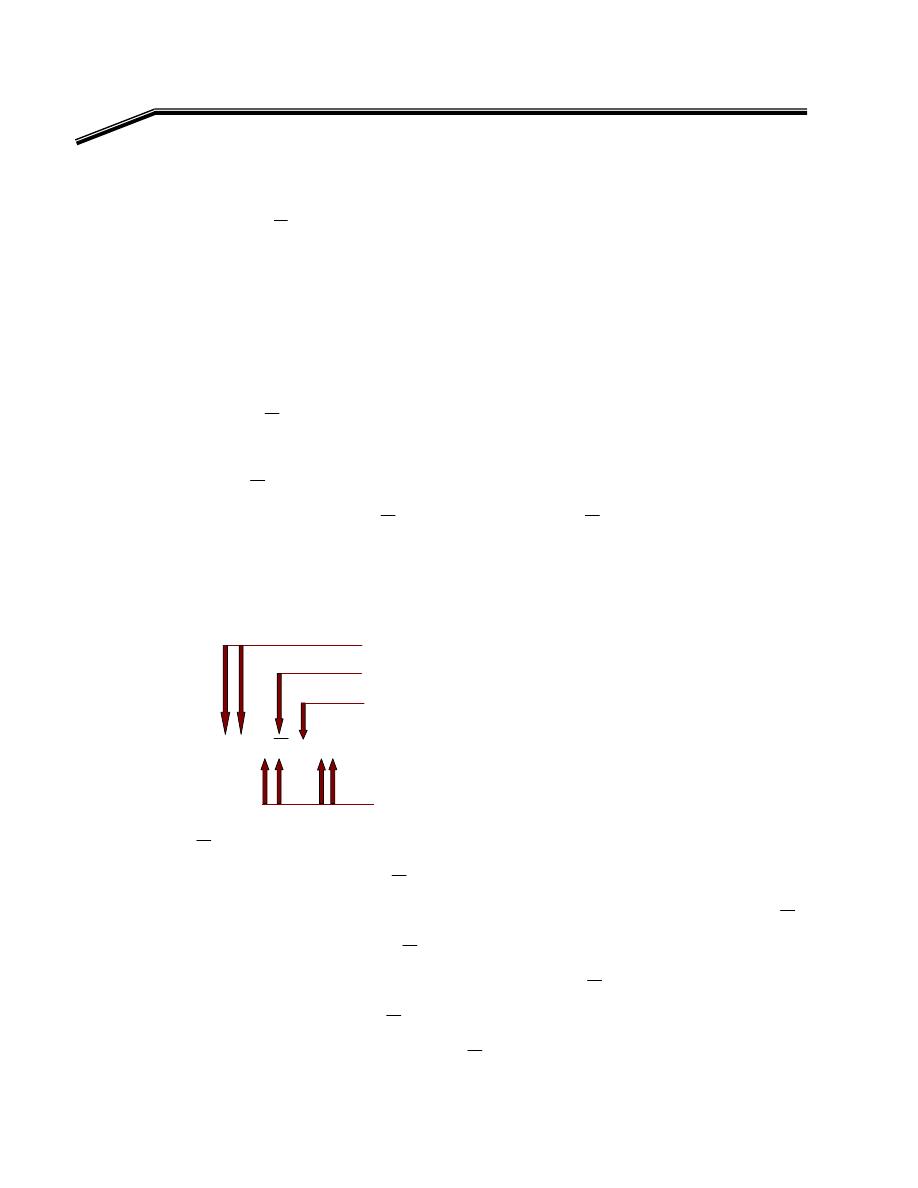

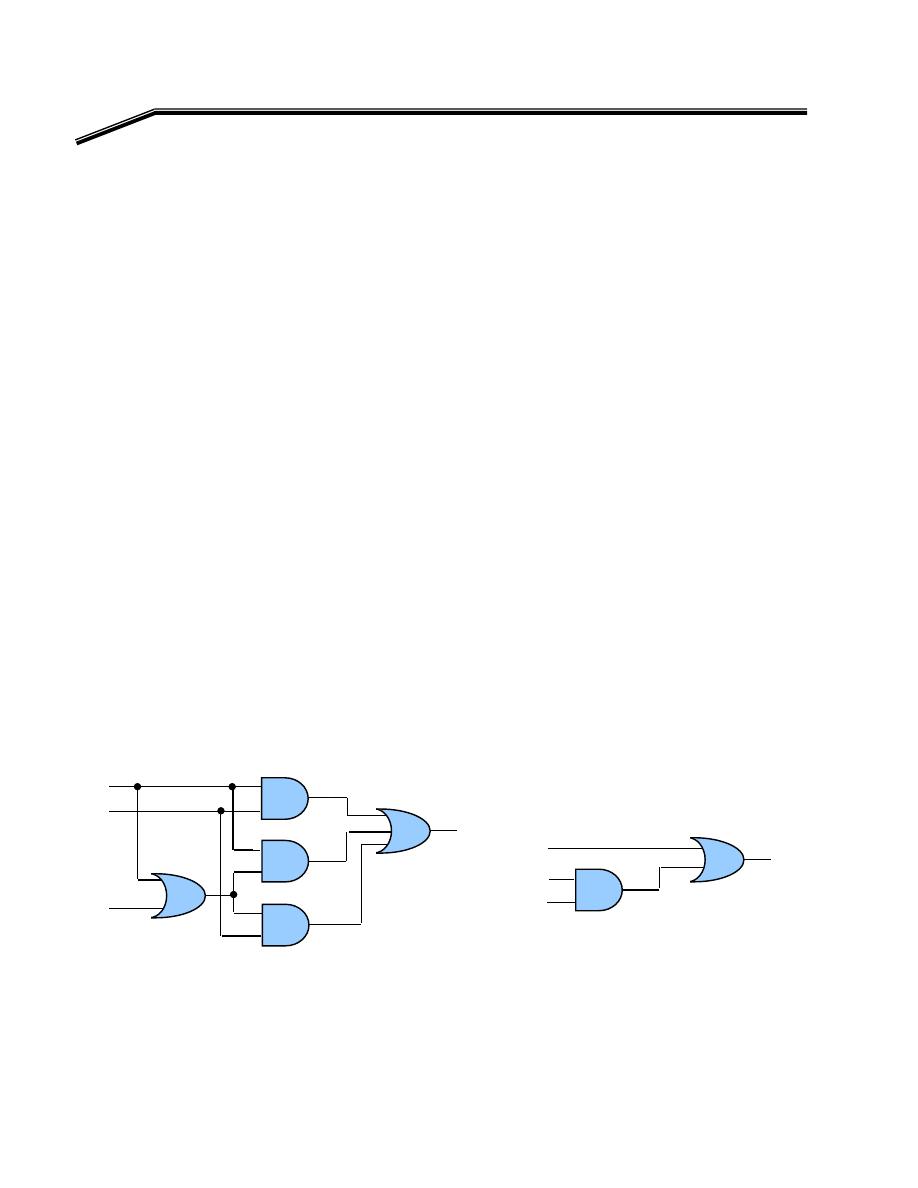

אאאאאא

אא

אאאאאאאא،א

אא

K

F

٢

J

٣٢

E

אא

אא

אא

F

א

F

E

E

אאא،

אא

F

א

F

E

KE

F

٢

J

٣٢

E

אאא

F

٢

J

٥

E

K

אא

אא

א،

A

,

B, C

،

אאא

K

A

B

C

F

E

Y

Y

A

B

F

E

C

אא

٧٤١

א

א

אאאא

א

-

٧٥

-

F

٢

J

٦

WE

אאאאאאא

א

K

ABC

BC

A

C

B

A

C

B

A

Y

+

+

+

=

א

W

،אאאא،אאא

W

)

ABC

BC

A

(

)

C

B

A

C

B

A

(

Y

+

+

+

=

)

A

A

(

BC

)

C

C

(

B

A

+

+

+

=

א

٦

W

1

BC

1

B

A

Y

•

+

•

=

א

٤

אאא

W

BC

B

A

Y

+

=

F

٢

J

٤٢

E

אא

אא

K

F

٢

J

٤٢

E

אאא

F

٢

J

٦

E

K

B

A

C

Y

C

Y

A

B

F

E

F

E

אא

٧٤١

א

א

אאאא

א

-

٨٥

-

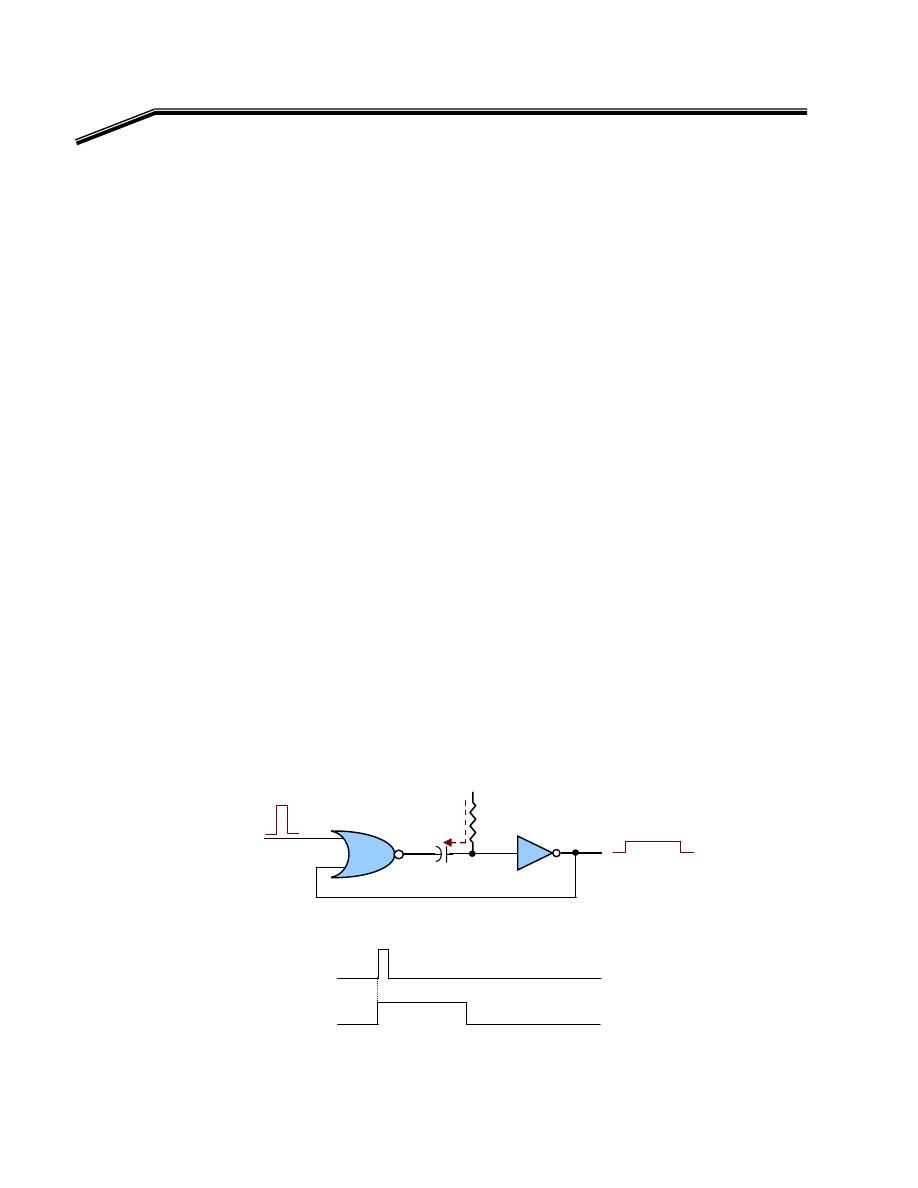

١

E

אאא

X

א

AND

אא

A,B

،

א

אא

J

١

K

J

١

٢

E

אאא

X

א

OR

אא

A,B

،

א

אא

J

١

K

٣

E

אאא

X

א

NAND

אא

A,B

،

א

אא

J

٢

K

J

٢

X

A

B

A

B

X

אא

٧٤١

א

א

אאאא

א

-

٩٥

-

٤

E

אאא

X

א

NOR

אא

A,B

אא،

אא

J

٣

K

J

٣

٥

E

אאא

X

א

XOR

אא

A,B

אא،

אא

J

٣

K

٦

E

אאא

X

א

XNOR

אא

A,B

אא،

אא

J

٣

K

٧

E

אאאאא

J

٤K

J

٤

A

B

X

C

Y

A

B

אא

٧٤١

א

א

אאאא

א

-

٠٦

-

٨

E

אאאא

אאאא

W

a)

B

A

B

A

+

b)

c)

d)

٩

E

אאאאאא

K

א

א

Y

C

B

A

٠

٠

٠

٠

١

١

٠

٠

٠

٠

١

٠

١

١

١

٠

٠

٠

٠

١

١

١

٠

١

٠

٠

١

١

١

١

١

١

٠١

E

אאאאא

W

a)

b)

c)

d)

١١

E

אאאאאאא

W

a)

b)

b)

d)

BC

A

AB

AB

+

+

)

D

C

(

B

A

+

)]

C

B

(

D

C

[

B

A

+

+

+

C

)

B

A

(

+

)

C

B

)(

B

A

(

+

+

)

B

A

AC

(

A

+